#### PROPRIETARY RIGHTS STATEMENT

THIS DOCUMENT CONTAINS INFORMATION, WHICH IS PROPRIETARY TO THE ASSUME CONSORTIUM. NEITHER THIS DOCUMENT NOR THE INFORMATION CONTAINED HEREIN SHALL BE USED, DUPLICATED OR COMMUNICATED BY ANY MEANS TO ANY THIRD PARTY, IN WHOLE OR IN PARTS, EXCEPT WITH THE PRIOR WRITTEN CONSENT OF THE ASSUME CONSORTIUM THIS RESTRICTION LEGEND SHALL NOT BE ALTERED OR OBLITERATED ON OR FROM THIS DOCUMENT. THE RESEARCH LEADING TO THESE RESULTS HAS RECEIVED FUNDING FROM VARIOUS NATIONAL AUTHORITIES IN THE FRAMEWORK OF THE ITEA 3 PROGRAMME (PROJECT NUMBER 14014).

Affordable Safe & Secure Mobility Evolution

# Advanced Concurrent Static Analysis Toolkit Description

Deliverable D5.2

| Deliverable Information |                   |                      |                     |  |

|-------------------------|-------------------|----------------------|---------------------|--|

| Nature                  | Document          | Dissemination Level  | Public              |  |

| Project                 | ASSUME            | Project Number 14014 |                     |  |

| Deliverable ID          | D5.2              | Date                 | 31.08.2018          |  |

| Status                  | Final             | Version              | v13                 |  |

| Contact Person          | Reinhold Heckmann | Organisation         | AbsInt GmbH         |  |

| Phone                   | ++49-681-38360-25 | E-Mail               | heckmann@absint.com |  |

# **Author Table**

| Name                             | Partner        | Email                                   |  |  |  |

|----------------------------------|----------------|-----------------------------------------|--|--|--|

| Reinhold Heckmann                | AbsInt         | heckmann@absint.com                     |  |  |  |

| Arturo Tejada Ruiz               | TNO            | arturo.tejadaruiz@tno.nl                |  |  |  |

| Mladen Skelin                    | TU/e           | m.skelin@tue.nl                         |  |  |  |

| Anja Stoll                       | MES            | anja.stoll@model-engineers.com          |  |  |  |

| Sebastian Ottlik                 | FZI            | ottlik@fzi.de                           |  |  |  |

| Philipp Sieweck                  | UKiel          | psi@informatik.uni-kiel.de              |  |  |  |

| Philipp Reinkemeier              | OFFIS          | philipp.reinkemeier@offis.de            |  |  |  |

| Ralf Vogler                      | тим            | ralf.vogler@tum.de                      |  |  |  |

| Antoine Miné Sorbonne University |                | Antoine.Mine@ens.fr                     |  |  |  |

| Helmut Seidl                     | ТИМ            | seidl@in.tum.de                         |  |  |  |

| Hassan Salehe Matar              | Koç University | hmatar@ku.edu.tr                        |  |  |  |

| Anton Paule                      | FZI            | paule@fzi.de                            |  |  |  |

| Jens-Peter Rohrlack              | MES            | jens-peter.rohrlack@model-engineers.com |  |  |  |

| Rifat Atar                       | Ericsson       | rifat.atar@ericsson.com                 |  |  |  |

# **Change and Revision History**

| Version | Date       | Reason for Change                | Affected sections |

|---------|------------|----------------------------------|-------------------|

| v01     | 23.05.2018 | Initial version                  | All               |

| v02     | 15.06.2018 | Update of SDF section            | 2.3               |

| v03     | 22.06.2018 | Update of PLAATO section         | 2.2               |

| v04     | 25.06.2018 | Update of EmbedSanitizer section | 5.1               |

| v05     | 25.06.2018 | New section on DRDCheck Hybrid   | 5.4               |

| v06     | 25.06.2018 | Update of C-SAPP section 4       |                   |

| v07     | 27.06.2018 | Update of Goblint section 3.2    |                   |

| v08     | 28.06.2018 | Update of Gropius section 3.1    |                   |

| v09     | 11.07.2018 | Update of RTANA2 section         | 2.4               |

| v10     | 16.07.2018 | Update of Astrée section         | 3.3               |

| v11     | 20.07.2018 | Update of M-XRAY section 2.1     |                   |

| v12     | 23.07.2018 | Finalization for internal review | All               |

| v13     | 31.08.2018 | Finalization for delivery All    |                   |

# **Table of Contents**

| Αu  | THOR TAB          | 3LE                                                                        | 2  |

|-----|-------------------|----------------------------------------------------------------------------|----|

| Сн  | ANGE AND          | REVISION HISTORY                                                           |    |

| ΤΑ  |                   | DNTENTS                                                                    | 4  |

| Lis | T OF FIGU         | RES                                                                        | 7  |

| Lis | т ог Авві         | REVIATIONS                                                                 | 9  |

| 1.  | Executi           | IVE SUMMARY                                                                | 11 |

| 2.  | ANALYS            | ES ON MODEL LEVEL                                                          | 12 |

| 2   | 2.1. M-X          | (RAY: SIMULINK MODEL REFACTORING SUPPORT                                   | 13 |

|     | 2.1.1.            | Introduction                                                               |    |

|     | 2.1.2.            | Methodology                                                                |    |

|     | 2.1.3.            | Work done in the ASSUME project                                            |    |

|     | 2.1.3.1           |                                                                            |    |

|     | 2.1.3.2           | 2. Metrics for coupling                                                    | 14 |

|     | 2.1.3.3           | 3. Effective interface metric                                              | 15 |

| 2   | 2.2. PLA          | ATO: PLATFORM ARCHITECTURE ANALYSIS TOOLS                                  | 16 |

|     | 2.2.1.            | Introduction                                                               | 16 |

|     | 2.2.2.            | Methodology                                                                | 17 |

|     | 2.2.2.1           | 1. Inputs                                                                  | 17 |

|     | 2.2.2.2           |                                                                            |    |

|     | 2.2.2.3           |                                                                            |    |

|     | 2.2.3.            | Current status and future development                                      |    |

|     | 2.2.4.            | Use Cases and KPIs                                                         |    |

| 2   | 2.3. SDF          | F FOR FREE (SDF <sup>3</sup> ): PERFORMANCE ANALYSIS OF DATAFLOW MODELS    | 21 |

|     | 2.3.1.            | Introduction                                                               |    |

|     | 2.3.2.            | Related work                                                               | 22 |

|     | 2.3.3.            | Preliminaries                                                              |    |

|     | 2.3.3.1           | 1. (max,+) Algebra                                                         | 23 |

|     | 2.3.3.2           | -,                                                                         |    |

|     | 2.3.3.3           | ( . , , , , ,                                                              |    |

|     | 2.3.3.4           |                                                                            |    |

|     | 2.3.3.5           |                                                                            |    |

|     | 2.3.4.<br>2.3.4.1 | Throughput Analysis of Hierarchical SDF Models                             |    |

|     | 2.3.4.1           | 5                                                                          |    |

|     | 2.3.4.3           | •                                                                          |    |

|     | 2.3.5.            | Compositionality in Synchronous Dataflow: Modular Performance Analysis fro |    |

|     |                   | hical SDF Graphs                                                           |    |

|     | 2.3.6.            | Analysis flow                                                              |    |

|     | 2.3.7.            | Conclusion                                                                 |    |

|     | 2.3.8.            | Current status                                                             |    |

|     | 2.3.9.            | Use case                                                                   |    |

| ~   |                   | ANA2: SYSTEM-LEVEL TIMING ANALYSIS OF REAL-TIME SYSTEM MODELS              |    |

| 2   |                   |                                                                            |    |

|     | 2.4.1.            | Introduction                                                               |    |

|    | 2.4.2.   | Input                                                                              | . 38 |  |  |

|----|----------|------------------------------------------------------------------------------------|------|--|--|

|    | 2.4.3.   | Method description                                                                 | . 39 |  |  |

|    | 2.4.4.   | Interface to concurrency defect analyses                                           | 41   |  |  |

|    | 2.4.5.   | Current status and future development                                              | . 42 |  |  |

|    | 2.4.5.1  |                                                                                    |      |  |  |

|    | 2.4.5.2  |                                                                                    |      |  |  |

|    | 2.4.5.3  | .3. Compositional Analysis Strategy Combining State-based and Analytical Methods46 |      |  |  |

| 3. | STATIC A | ANALYSIS OF C CODE FOR CONCURRENCY ERRORS                                          | 50   |  |  |

| 3  | .1. Gro  | DPIUS                                                                              | 50   |  |  |

| 0. |          |                                                                                    |      |  |  |

|    | 3.1.1.   | Input                                                                              |      |  |  |

|    | 3.1.2.   | Output                                                                             |      |  |  |

|    | 3.1.3.   | Method description                                                                 |      |  |  |

|    | 3.1.4.   | Ranking heuristic                                                                  |      |  |  |

|    | 3.1.5.   | What changed between D5.0 and D5.1                                                 |      |  |  |

|    | 3.1.6.   | What changed since D5.1                                                            |      |  |  |

|    | 3.1.7.   | Use-Cases                                                                          |      |  |  |

|    | 3.1.8.   | KPI Status                                                                         | 54   |  |  |

| 3. | .2. Goe  | BLINT                                                                              | 55   |  |  |

|    | 3.2.1.   | Input and Output                                                                   | . 55 |  |  |

|    | 3.2.2.   | Configuration                                                                      | . 56 |  |  |

|    | 3.2.3.   | Method description                                                                 | . 57 |  |  |

|    | 3.2.4.   | Analysis of Asynchronous Programs                                                  | . 57 |  |  |

|    | 3.2.5.   | Scalability                                                                        | . 57 |  |  |

|    | 3.2.6.   | Improvements since D5.0 and KPI Status                                             |      |  |  |

| 3. | .3. Ast  | RÉE                                                                                | . 58 |  |  |

|    | 3.3.1.   | Input and Output                                                                   | 58   |  |  |

|    | 3.3.2.   | Features of Asynchronous Programs                                                  |      |  |  |

|    | 3.3.2.1  | , .                                                                                |      |  |  |

|    | 3.3.2.2  | 2. Synchronization Objects                                                         | 60   |  |  |

|    | 3.3.3.   | Analysis of Asynchronous Programs                                                  | 61   |  |  |

|    | 3.3.4.   | Execution Model                                                                    | . 62 |  |  |

|    | 3.3.5.   | Abstraction of Concrete Behaviour                                                  | . 64 |  |  |

|    | 3.3.6.   | Error Reporting                                                                    | . 64 |  |  |

|    | 3.3.7.   | Improvements during the Project and KPI Status                                     | 65   |  |  |

| 4. | ANALYSI  | s of Hardware-Dependent Software                                                   | . 67 |  |  |

|    |          | LYSIS OF ASYNCHRONOUS AND CONCURRENT HW DEPENDENT SW                               |      |  |  |

| 4. |          |                                                                                    |      |  |  |

|    | 4.1.1.   | Input                                                                              |      |  |  |

|    | 4.1.2.   | Invocation                                                                         |      |  |  |

|    | 4.1.3.   | Method description                                                                 |      |  |  |

|    | 4.1.4.   | Output                                                                             |      |  |  |

|    | 4.1.5.   | Changes compared to D5.0 and future development                                    |      |  |  |

|    | 4.1.6.   | KPI status                                                                         | 72   |  |  |

| 4. | .2. DEA  | DLOCK ANALYSES FOR REAL-TIME EMBEDDED SYSTEMS                                      | 72   |  |  |

|    | 4.2.1.   | Method description                                                                 | . 73 |  |  |

|    | 4.2.2.   | Algorithm                                                                          | . 74 |  |  |

| 5.  | RACE DE | ETECTION BY INSTRUMENTATION                                      | 77 |

|-----|---------|------------------------------------------------------------------|----|

| 5   | .1. Емв | BEDSANITIZER: RACE DETECTION FOR ARMV7 POSIX-THREAD APPLICATIONS | 77 |

|     | 5.1.1.  | Introduction                                                     | 77 |

|     | 5.1.2.  | Method                                                           | 77 |

|     | 5.1.2.1 |                                                                  |    |

|     | 5.1.2.2 | 2. Installation                                                  | 79 |

|     | 5.1.3.  | Evaluation                                                       | 79 |

|     | 5.1.3.1 |                                                                  |    |

|     | 5.1.3.2 |                                                                  |    |

|     | 5.1.4.  | Uses cases and requirements                                      | 81 |

|     | 5.1.5.  | Status w.r.t. KPIs                                               | 81 |

| 5   | .2. GOL | DILOCKS                                                          | 82 |

| 5   | .3. Fas | тТкаск                                                           | 82 |

| 5   | .4. DRI | ОСнеск Нувгід                                                    | 83 |

|     | 5.4.1.  | Introduction                                                     |    |

|     | 5.4.2.  | Method                                                           | 83 |

|     | 5.4.3.  | Evaluation                                                       | 83 |

| 6.  | CONCLU  | SIONS AND DISCUSSION                                             | 84 |

| Ref | ERENCES |                                                                  | 85 |

# **List of Figures**

| FIGURE 1: M-XRAY WORKFLOW                                                                                                | 3 |

|--------------------------------------------------------------------------------------------------------------------------|---|

| FIGURE 2: EXAMPLE OF SUBSYSTEM WITH TWO INHERENT COMPONENTS HIGHLIGHTED WITH COLOURED RECTANGLES                         | ł |

| FIGURE 3: REFACTORING EXAMPLE USING INCOHERENCE METRIC ON SUBSYSTEM WHERE DEPENDENCIES<br>ARE HIDDEN BY GOTO+FROM BLOCKS |   |

| FIGURE 4: EXCERPT FROM M-XRAY EXCEL REPORT WITH QUALITY METRICS FOR NUMBER OF IN- AND OUTPORTS                           | 5 |

| FIGURE 5: EXAMPLE OF EFFECTIVE INTERFACE COMPUTATION                                                                     | 5 |

| FIGURE 6: PLAATO INTERFACE EXAMPLE                                                                                       | ; |

| FIGURE 7: PLAATO'S CURRENT STRUCTURE                                                                                     | 7 |

| FIGURE 8: EXAMPLE OF PLAATO'S MATLAB GUI                                                                                 | 3 |

| FIGURE 9: OVERVIEW OF TNO'S CONTRIBUTION TO THE ASSUME PROJECT. SEE DELIVERABLE 1.4 FOR DETAILS                          |   |

| FIGURE 10: EXAMPLE OF AN SDF GRAPH24                                                                                     | ŀ |

| FIGURE 11: EXAMPLE OF A HIERARCHICAL SDF GRAPH                                                                           | 5 |

| FIGURE 12: AN FSM-SADF GRAPH27                                                                                           | 7 |

| FIGURE 13: COMPOSITIONALITY IN SDF                                                                                       | 3 |

| FIGURE 14: DSSF PROFILES                                                                                                 | ŀ |

| FIGURE 15: FSM-SADF PERFORMANCE MODEL FOR DSSF                                                                           | 5 |

| FIGURE 16: SDF <sup>3</sup> ANALYSIS FLOW                                                                                | 5 |

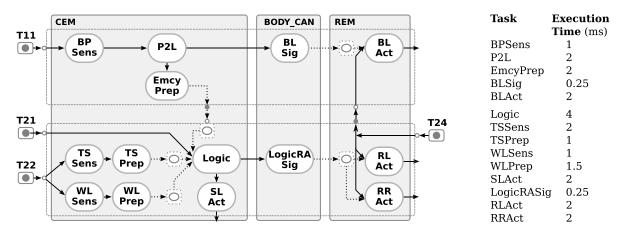

| FIGURE 17: TASK NETWORK EXAMPLE                                                                                          | ) |

| FIGURE 18: STATE REPRESENTATION FOR EVENT MODEL (LEFT) AND RESOURCES (RIGHT)                                             | ) |

| FIGURE 19: SYSTEM STATE REPRESENTATION                                                                                   | I |

| FIGURE 20: FLOW DIAGRAM OF COMPOSITIONAL COMBINED REAL-TIME ANALYSIS                                                     | , |

| FIGURE 21: CASE-STUDY: EXTERIOR LIGHT MANAGEMENT SYSTEM                                                                  | , |

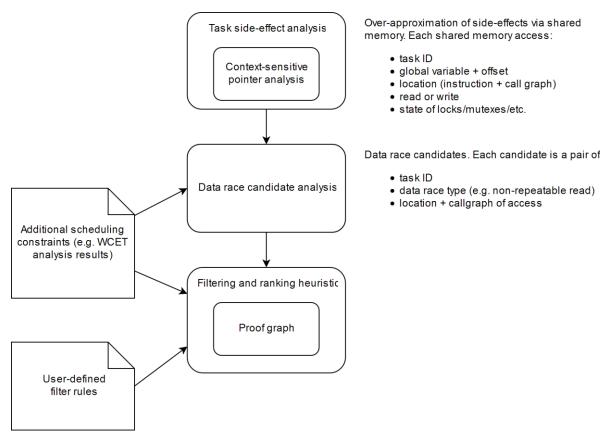

| FIGURE 22: ANALYSIS STEPS IN GROPIUS                                                                                     | 2 |

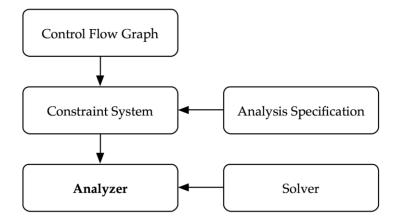

| FIGURE 23: STRUCTURE OF GOBLINT (SEE [13])                                                                               | 5 |

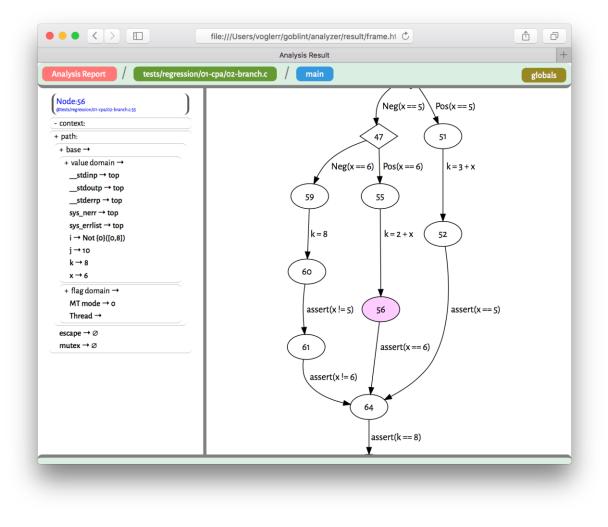

| FIGURE 24: GOBLINT'S HTML OUTPUT                                                                                         | 5 |

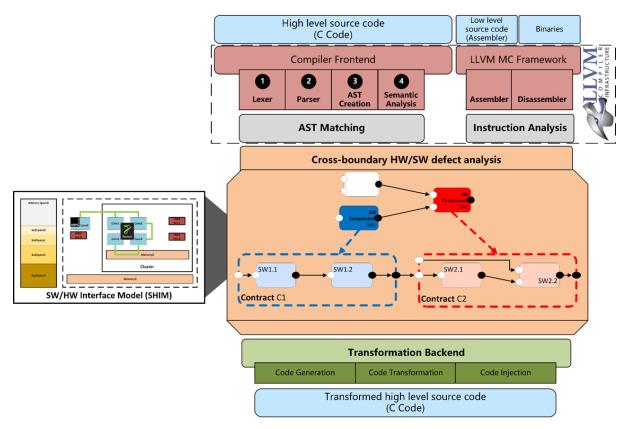

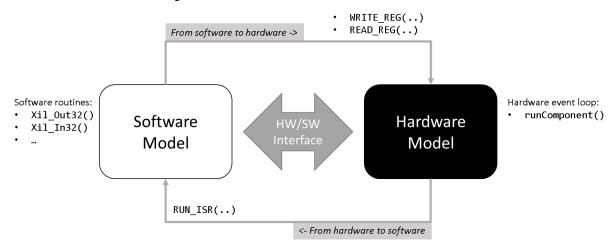

| FIGURE 25: ANALYSES OF HARDWARE-DEPENDENT SOFTWARE (HDS) WORKFLOW                                                        | 3 |

| FIGURE 26: SPECIFICATION OF THE HW/SW INTERACTION                                                                        | ) |

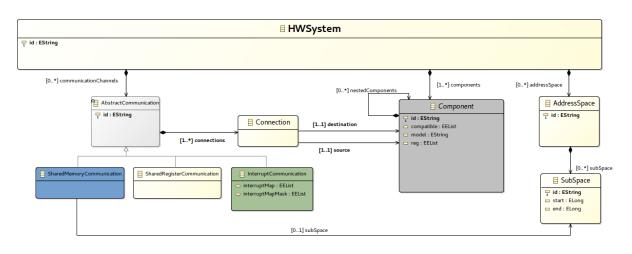

| FIGURE 27: EXCERPT FROM THE SW/HW INTERFACE METAMODEL                                                                    | ) |

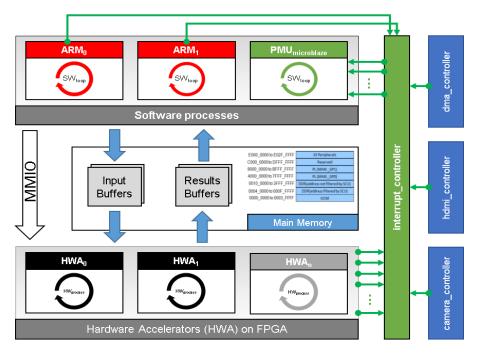

| FIGURE 28: PLATFORM MODEL FOR THE FZI_UC01 DEMONSTRATOR                                                                  | ) |

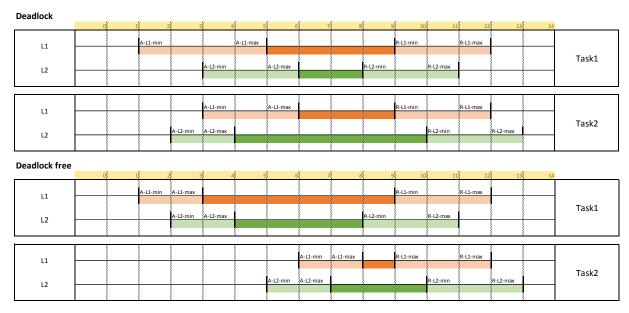

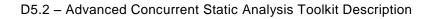

| FIGURE 29: TWO SCENARIOS WITH INTERLEAVINGS BETWEEN TWO TASKS                                                            | 5 |

| FIGURE 30: CALCULATED TIMING INTERVALS FOR THE TWO SCENARIOS                                                             | 5 |

|                                                                                                                          |   |

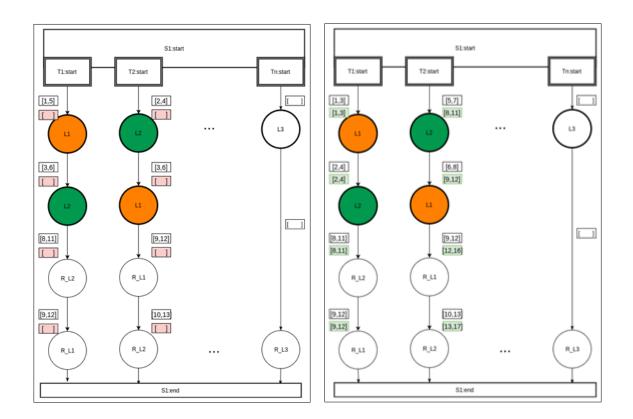

| FIGURE 31: HIGH LEVEL ABSTRACTION OF THREADSANITIZER AND EMBEDSANITIZER IN LLVM/CLANG.                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| (A) THREADSANITIZER: ESSENTIAL LLVM MODULES FOR RACE DETECTION. (B) EMBEDSANITIZER: SAME                                                                |

| MODULES MODIFIED TO INSTRUMENT AND DETECT RACES FOR 32-BIT ARM                                                                                          |

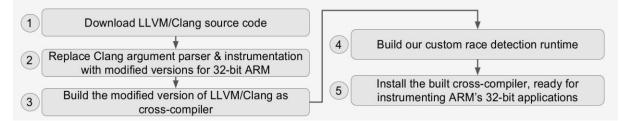

| FIGURE 32: SHOWING THE AUTOMATED PROCESS FOR THE INITIAL BUILD OF EMBEDSANITIZER                                                                        |

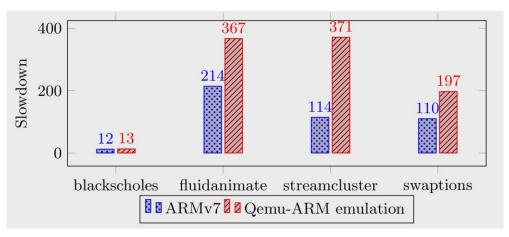

| FIGURE 33: SLOWDOWN COMPARISON OF RACE DETECTION ON ARMV7 VS ON QEMU-ARM                                                                                |

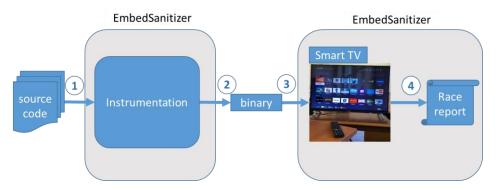

| FIGURE 34: ALTERNATIVE OVERVIEW OF EMBEDSANITIZER WHEN USED TO DETECT DATA RACES IN COLLABORATOR'S 32-BIT ARMV7 SMART TV SOFTWARE FOR USE CASE ARC_UC02 |

|                                                                                                                                                         |

# **List of Abbreviations**

| ADAS        | Advanced Driver Assistance Systems                                       |  |

|-------------|--------------------------------------------------------------------------|--|

| ADAS<br>API | Advanced Driver Assistance Systems<br>Application Programming Interface  |  |

| AST         |                                                                          |  |

|             | Abstract Syntax Tree                                                     |  |

| BCET        | Best-Case Execution-Time                                                 |  |

| BSF         | Breadth-First Search                                                     |  |

| CFG         | Control Flow Graph                                                       |  |

| CIL         | C Intermediate Language                                                  |  |

| CIVL        | Concurrency Intermediate Verification Language                           |  |

| CPU         | Central Processing Unit                                                  |  |

| CSDF        | Cycle-Static DataFlow                                                    |  |

| DMA         | Direct Memory Access                                                     |  |

| DSSF        | Deterministic SDF with Shared FIFOs                                      |  |

| EA          | Enterprise Architect                                                     |  |

| ECU         | Electronic Control Unit                                                  |  |

| ENS         | École Normale Supérieure (Paris)                                         |  |

| FCFS        | First-Come, First-Served                                                 |  |

| FIFO        | First In, First Out (queue)                                              |  |

| FSM         | Finite-State Machine                                                     |  |

| FSM-SADF    | Finite-State Machine-based Scenario-Aware DataFlow                       |  |

| GUI         | Graphical User Interface                                                 |  |

| HdS         | Hardware-dependent Software                                              |  |

| HSDF        | Homogeneous SDF                                                          |  |

| HTML        | HyperText Markup Language                                                |  |

| HW          | Hardware                                                                 |  |

| HWA         | Hardware Accelerator                                                     |  |

| IDE         | Integrated Development Environment                                       |  |

| I/O         | Input/Output                                                             |  |

| JSON        | JavaScript Object Notation                                               |  |

| J∨M         | Java Virtual Machine                                                     |  |

| LCG         | Linear Constraint Graph                                                  |  |

| LLBMC       | Low-Level Bounded Model Checker                                          |  |

| LLVM        | (collection of modular and reusable compiler and toolchain technologies) |  |

| LTL         | Linear Temporal Logic                                                    |  |

| MMIO        | Memory Mapped Input/Output                                               |  |

| MoC         | Model of Computation                                                     |  |

| Mutex       | Mutual exclusive lock                                                    |  |

| M-XRAY      | (static analysis tool for Simulink models)                               |  |

| OIL         | OSEK Implementation Language                                             |  |

|             |                                                                          |  |

| OS               | Operating System                                                   |

|------------------|--------------------------------------------------------------------|

| PLAATO           | Platform Architecture Analysis Tool                                |

| RTANA2           | (tool for system-level timing analysis of real-time system models) |

| SDF              | Synchronous DataFlow                                               |

| SDF <sup>3</sup> | (tool for performance analysis of dataflow models)                 |

| SME              | Small or Medium Enterprise                                         |

| SW               | Software                                                           |

| тим              | Technische Universität München                                     |

| TU/e             | Technische Universiteit Eindhoven                                  |

| UPMC             | Université Pierre et Marie Curie                                   |

| WCET             | Worst-Case Execution-Time                                          |

| WP               | Work Package                                                       |

| XML              | Extensible Markup Language                                         |

# 1. Executive Summary

This deliverable provides a description of the analysis tools proposed or used in WP5 of the ASSUME project. The common aim of these tools is the analysis of concurrent behaviour. Their descriptions are grouped according to what they analyse and how they do this.

The first group consists of four tools performing analysis on the model level (Section 2). It comprises M-XRAY providing Simulink model refactoring support (Section 2.1), PLAATO performing platform architecture analysis (Section 2.2), SDF<sup>3</sup> for performance analysis of dataflow models (Section 2.3), and RTANA2 for system-level timing analysis of real-time system models (Section 2.4).

The second group consists of three tools for static analysis of C code for concurrency error (Section 3). It comprises Gropius (Section 3.1), Goblint (Section 3.2), and Astrée (Section 3.3). Static analysis means that the code is analysed without executing it. Its results are valid for all executions with all inputs.

The third group deals with analysis of hardware-dependent software (Section 4). It contains the C-SAPP tool for analysis of asynchronous and concurrent hardware-dependent software (Section 4.1) and a related method for deadlock analysis of real-time embedded systems (Section 4.2).

The last group (Section 5) comprises several related approaches for race detection by instrumentation. All these approaches produce a binary executable augmented by instrumentation code that detects concurrency errors while the instrumented program is running and produces a report about its findings.

This deliverable D5.2 is the third in a series of deliverables. Its predecessors D5.0 and D5.1 presented the status of the WP5 tools after the first and second year of the project, respectively. D5.2 presents the status at the end of the project, i.e. after three years of work in ASSUME.

# 2. Analyses on Model Level

This section presents four tools with the common property that they perform analysis on model level.

The M-XRAY tool by MES is a static analysis tool for Simulink models, which is extended in ASSUME to support the refactoring of models towards multi-core concurrency by computing and representing dependencies (Section 2.1).

The Platform Architecture Analysis Tool PLAATO is developed by TNO with the goal to provide researchers and designers with the ability of assessing a given HW/SW architecture using objective criteria such as failure probabilities, mean time to failure, etc. (Section 2.2).

The SDF<sup>3</sup> tool for performance analysis of dataflow models has been developed by TU/e. In ASSUME, the analysis of finite-state machine-based scenario-aware dataflow is extended to improve precision in the case where the selection of the scenario to be activated next depends on time (Section 2.3).

The RTANA2 tool performs system-level timing analysis of real-time system models. It is being extended by OFFIS so that it can compute properties of real-time models such as response times per task, end-to-end latencies of functional chains of tasks, maximum number of pending activations per task, and pre-emption relationships between tasks for each resource (Section 2.4).

# 2.1. M-XRAY: Simulink Model Refactoring Support

# 2.1.1. Introduction

During the lifetime of the ASSUME project, MES extended M-XRAY – its static analysis tool for Simulink models – to support the refactoring of models towards multi-core concurrency. First coupling and cohesion were defined for the dedicated domain of Simulink models in order to support industrial applications. Second, we designed an algorithm to compute dependencies between subsystems. Third, an appropriate representation of the dependencies was introduced to support the planning of refactoring and the assessment of design options.

## 2.1.2. Methodology

M-XRAY analyzes Simulink models at the level of individual subsystems as well as aggregated results for the complete model. M-XRAY generates different metrics to evaluate different quality aspects of the model, like the complexity of individual subsystems.

To evaluate the aspect of coupling and cohesion and visualize dependencies, M-XRAY computes specific metrics highly correlated to this aspect. These metrics are used by M-XRAY for two purposes: Firstly, the metrics can be used to guide the model developer to parts of the model that are violating specified quality standards. Secondly, the metrics are used for appropriate representations that can give further information of how to start or conduct a refactoring in terms of multi-core concurrency.

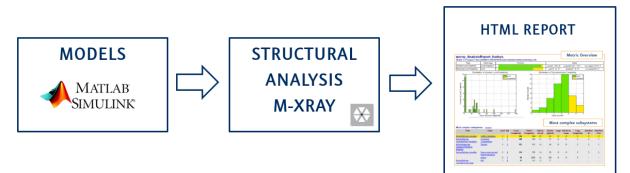

As shown in Figure 1 below, M-XRAY conducts the structural analysis of the given Simulink models and presents the described results in an HTML report.

Figure 1: M-XRAY workflow

# 2.1.3. Work done in the ASSUME project

## 2.1.3.1. Cohesion for Simulink models

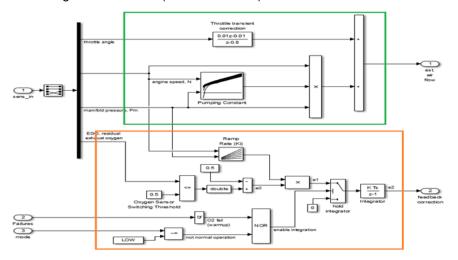

Different metrics have been evaluated by MES that are related to the quality aspect of cohesion. As part of the ASSUME project an *incoherence* metric was introduced in M-XRAY 3.1. This metric is based on the *tight cohesion* introduced in Mäurer et al. [1]. The goal is to identify subsystems that have a low cohesion and, thus, may be split up into multiple subsystems. The new subsystems make the different data flow components obvious, which is a useful information for refactoring, in particular in terms of multi-core concurrency. Imagine the subsystem from Figure 2 which has a low cohesion because, actually, two parallel components are mixed up in a single system (green and orange rectangles).

The *incoherence* metric of M-XRAY helps to detect this kind of subsystems. The incoherence is computed as the inverse of the tight cohesion from Mäurer et al. [1]. Thus, if all blocks of a

subsystem are somehow connected by signal paths, the subsystem has a low incoherence (= high cohesion). If there are separate groups of blocks that are not connected by signal paths, the subsystem has a high incoherence (= low cohesion).

Figure 2: Example of subsystem with two inherent components highlighted with coloured rectangles

The incoherence metric gives a rough estimate of the parallel divisibility of a subsystem. For the example subsystem from Figure 2, the incoherence metric is approximately 2, which gives a good estimate of the parallel divisibility. Figure 3 gives another nice application scenario in terms of identification of parallel components with subsequent refactoring. Due to the extensive use of *Goto+From* blocks, the dependencies between the individual blocks are completely obscured. For this subsystem M-XRAY's incoherence metric is approx. 3, so there should be roughly 3 inherent parallel components. The incoherence metric also helps to identify these components. After refactoring in the model editor, the data flow and separated components are made completely obvious (right part of Figure 3). Thus, the incoherence metric can especially guide the refactoring for cases where the separability of a subsystem is very hard to estimate manually in advance.

Figure 3: Refactoring example using incoherence metric on subsystem where dependencies are hidden by Goto+From blocks

# 2.1.3.2. Metrics for coupling

As a first supplement to the incoherence metric introduced in Release 3.1, quality metrics for the most direct and obvious forms of subsystem coupling were added in M-XRAY 3.2: Count of

subsystem inports and subsystem outports. These simple but important quality metrics help to assure quality standards like ISO 26262 and their demand for a 'Restricted size of interfaces'. A small interface in terms of inports and outports is a prerequisite for a fast refactoring in terms of multi-core concurrency. Therefore M-XRAY predefines quality metrics for the number of inports and outports. For quality metrics, thresholds can be set and surveyed easily from the M-XRAY reports. Figure 4 shows an excerpt from an M-XRAY Excel report where you can find quality metrics columns for the number of in- and outports of a subsystem together with a color shading for subsystem values above a quality threshold.

| А                                                                        | В                    | С         | D                   | E     | F                   | G          | Н        |

|--------------------------------------------------------------------------|----------------------|-----------|---------------------|-------|---------------------|------------|----------|

| General Info                                                             |                      |           |                     |       |                     | Quality Me | etrics   |

| Path                                                                     | Name                 | Info<br>🔽 | Quality<br>Failures | Level | Local<br>Complexity | Inports    | Outports |

| MxrayDemoModel/ComplexTopPart                                            | RegulatorOverview    |           | 0                   | 2     | 362                 | 35         | 5        |

| MxrayDemoModel/ComplexTopPart                                            | SecondBackupSystem   |           | 0                   | 2     | 603                 | 32         | 9        |

|                                                                          | MxrayDemoModel       | (Root)    | 1                   | 0     | 794                 | 10         | 8        |

| MxrayDemoModel/BackupFDRegulator/TimeRegulation/HRI_InflationControl/PRM | RegulatorOverview    |           | 0                   | 5     | 203                 | 5          | 5        |

| MxrayDemoModel                                                           | RegulatorOverview    |           | 0                   | 1     | 237                 | 5          | 5        |

| MxrayDemoModel                                                           | BackupFDRegulator    |           | 0                   | 1     | 566                 | 4          | 4        |

| MxrayDemoModel/BackupFDRegulator/TimeRegulation                          | HRI_InflationControl |           | 0                   | 3     | 482                 | 3          | 3        |

| MxrayDemoModel/BackupFDRegulator/TimeRegulation/HRI_InflationControl/PRM | MixedRegDupl         |           | 0                   | 6     | 379                 | 2          | 2        |

| N                                                                        | net ave net          |           | •                   | -     | 200                 | 2          | 4        |

Figure 4: Excerpt from M-XRAY Excel report with quality metrics for number of in- and outports

# 2.1.3.3. Effective interface metric

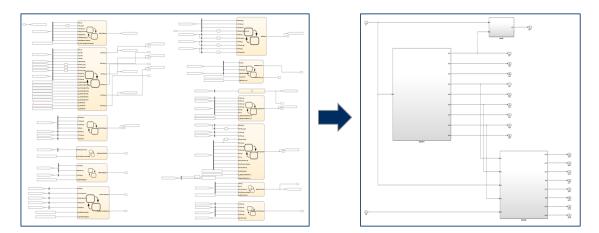

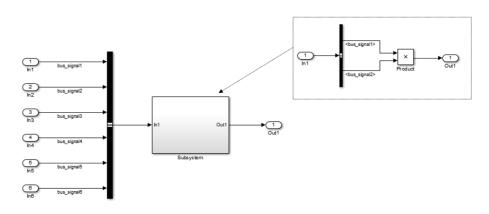

To extend the incoherence and interface count metrics already introduced in M-XRAY 3.1 and 3.2, M-XRAY has been extended as part of the ASSUME project to measure the 'effective interface' of Simulink subsystems. As Simulink subsystems can have input and output signals in the form of buses and as signals can be directly forwarded to subordinate subsystems, a key to understand the real coupling of a subsystem is to detect which input and output signals are effectively used or defined in a subsystem. To give a simple example, the subsystem from Figure 5 has an effective input interface size of two as only two of six input bus signals are effectively used in the subsystem.

Figure 5: Example of effective interface computation

# 2.2. PLAATO: Platform Architecture Analysis Tools

## 2.2.1. Introduction

In safety-critical domains such as automotive, railway, and avionics, even a small failure of a system might cause injury to or death of people. A number of international safety standards are introduced as guidelines for system suppliers to keep the risk of systems at an acceptable level, such as IEC 61508 (multiple domains), ISO 26262 (automotive domain), DO 254 (avionic domain), CENELEC railway standards (railway domain). In the automotive domain, currently the ISO 26262 standard, which is a goal-oriented standard for safety-critical systems within the domain of road vehicles, is the state of the art. This is, of course, the applicable standard for the Dutch (VDL) use case, which is the driver for TNO's developments in the ASSUME project.

After its introduction in 2011, ISO 26262 has attracted more and more attention in the automotive domain. There are more than 120 work products generated throughout the safety lifecycle suggested by this standard. This makes managing traceability and consistency of the information an absolute necessity for assuring safety and compliance. In order to be able to maintain the above-mentioned traceability when designing a vehicular system, it is important to have a well-structured process in place. This is already partly ensured when ISO 26262 is followed, however the norm still leaves a lot open for interpretation and in itself cannot guarantee the quality of a design process.

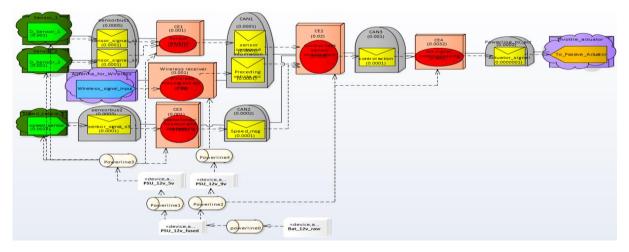

To aid in this process, TNO has developed a tool called Platform Architecture & Analysis Tool (PLAATO) using Enterprise Architect as front end to input hardware and software models (and eventually link them to requirements using an ISO 26262 template). An example of that interface is shown in Figure 6.

Figure 6: PLAATO Interface example

Based on this information, PLAATO is able to automatically generate fault trees and to perform reliability analysis on them (the analysis is performed in Matlab). The tool can also provide support advising the designer on where to possibly improve the architecture to increase its reliability (i.e. resilience to faults) in accordance with safety requirements.

# 2.2.2. Methodology

TNO uses an existing commercial tool called Enterprise Architect (EA) to perform system design and analysis in a structured way. To achieve this, a specific "way of working" was set up by customizing the EA user interface and by connecting it with several other software tools (e.g., Excel, Matlab, etc.). Enterprise Architect supports design and architecture of a system at several levels of abstraction. It also supports traceability to documentation, code simulation and centralisation of the design.

By making use of different diagrams that contain specific information for specific people, a natural layered and ordered representation of a system design can be presented to the user. This together with EA's tools for maintaining traceability ensure that documentation about the design, the design decisions, and other project information is kept very close to the actual system development.

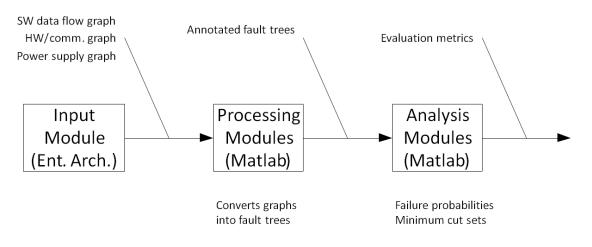

PLAATO's current structure is shown in Figure 7.

Figure 7: PLAATO's current structure

The above structure is complete. PLAATO is able to take an ADAS architecture and provide insight on its reliability, the main points of attention (e.g., which component failures are most critical), etc.

# 2.2.2.1. Inputs

PLAATO enables the user to deliver design input through a graphical representation of the system. To this end, three diagram templates have been added to those that are already available in Enterprise Architect:

- The first diagram is a function description diagram which shows which functions are present in the system. It captures information about what these functions do and the specific details about the information that is exchanged between these functions.

- The second diagram is a hardware description diagram, which captures details on how hardware is interconnected and what properties the hardware has. It also defines the interfaces that are used to communicate between hardware components, and properties that are required for fault tree generation (e.g. failure probability or failure rate).

- The third diagram is the deployment diagram. It contains information on how functions are deployed or mapped to the hardware. In this way an engineer can experiment with deploying multiple functions on one or more Electronic Control Units (ECUs) or shift tasks between ECUs.

## 2.2.2.2. Processing

When all information has been input correctly, it can be exported to Matlab for further processing. This is done by a plug-in to EA developed by TNO. The plug-in exports an ".m" file that can be interpreted by Matlab. This file is then executed, yielding a representation in Matlab of the system deployment.

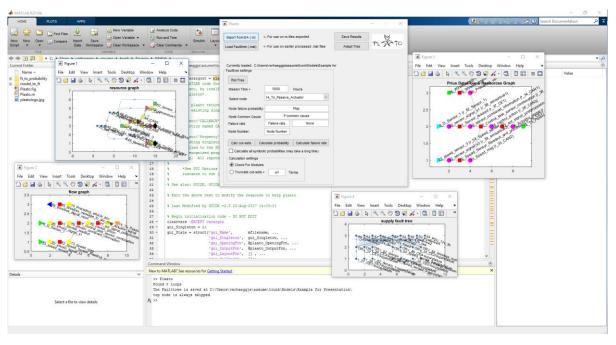

This representation allows the user to perform system analysis using a custom-made Matlab graphical user interface (GUI) (see Figure 8). This GUI can be used to generate a fault tree from the information that was entered in the model diagrams. When information is missing the tool will try to guide the user to enter all required information in EA.

Figure 8: Example of PLAATO's Matlab GUI

Once everything is complete, the fault tree can be analysed structurally as well as quantitatively. The structural analysis can be performed from a very early stage in the project as numbers are not strictly required – only the structure of the system will suffice. The quantitative analysis requires actual numbers such as failure rates or importance metrics of specific elements in the system. The GUI offers the user several options for both forms of analysis, however specific knowledge of the analysis methods is required to be able to interpret the results. A Matlab script subsequently processes these results to generate a static fault tree for a specific architectural component failure. (A fault tree describes the logical chain of component/subsystem faults that may trigger the considered architectural component failure [3]).

# 2.2.2.3. Output

PLAATO provides support to the system designer on deciding where to possibly improve the system's architecture. To this end, PLAATO offers a number of structural and quantitative analysis tools (running over the fault trees described above).

For structural analysis PLAATO offers the ability to look at:

- Modules in the tree. These are independent regions which will show that a certain part of the tree is independent of other parts of the tree. This can indicate containment regions, in which failures will not propagate to other branches of the tree. These modular regions can be emphasised by the tool.

- Minimal cut-sets. These are the smallest terms of the logical formula (Boolean expression) that corresponds with a tree. The expression describes how the Basic Events contribute to failure of the top node of the tree. Basic events are considered to be the smallest elements that can fail in the system. By looking at the expressions one gets insight in which events may result in system failures. If there are only few (or only one), this means that few faults (or only one) are required to trigger a system failure.

- The actual tree and its structure can be seen as a graphical representation. This will allow the analyst to visually inspect the tree.

For quantitative analysis, PLAATO offers the ability to look at:

- Failure probabilities of the basic events and how these are distributed with respect to each other.

- Failure probabilities of intermediate events and top event. These probabilities have to be calculated by finding the probability expression from the logical formula. The tool can perform these calculations.

- Importance metrics. The tool offers the ability to calculate importance metrics that will give information about the relative importance of the basic events in the tree. The tool supports the Birnbaum [55] and the Fussel-Vesely [56] importance measures.

The Matlab tool allows the user to store results in ".mat" files to be used for later analysis. Node properties can be adapted with the tool once the tree is generated. Additionally, one can build fault-trees directly in EA. A tree can then be export to an ".m" file and also be analysed in the tool. This way the fault-tree generation step can be skipped.

### 2.2.3. Current status and future development

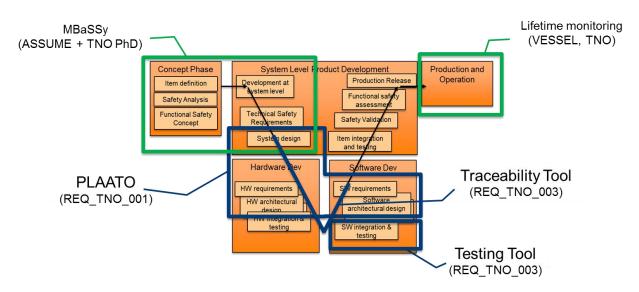

Figure 9 shows the main contributions of TNO to the ASSUME project, including PLAATO development (see Deliverable 1.4). At this point, the development of PLAATO has reached the stage of a mature prototype.

As shown in Figure 9, PLAATO mostly covers the left-hand side of the safety engineering Vcycle. The rest of the left side of the V-cycle (from Item Definition to System Design) will be covered by a second tool called MBaSSy: Model Based System Safety Analysis (MBaSSy). This tool is currently under development at TNO as part of a PhD project (partially supported by ASSUME). Once completed, MBaSSy will replace the PLAATO interface shown in Figure 6 with a SysML-compliant one, while keeping PLAATO's fault-tree analysis engine. It is expected that MBaSSy will cover the full V-cycle once completed, thus merging the three main contributions of TNO to this project (see Figure 9 and Deliverable 1.4 for details). For more information on MBaSSy, see Deliverable 3.4.

Figure 9: Overview of TNO's contribution to the ASSUME project. See Deliverable 1.4 for details

# 2.2.4. Use Cases and KPIs

All the activities described above are part of VDL's use case (TNO\_UC\_01) and support KPI1.1 (reduce the effort required to set up and employ an analysis tool).

# 2.3. SDF for free (SDF<sup>3</sup>): Performance Analysis of Dataflow Models

# 2.3.1. Introduction

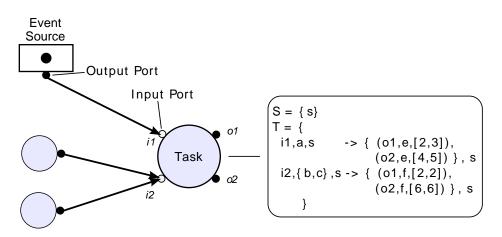

Dataflow models of computation are widely used to represent streaming systems. This is thanks to their simple graphical representation, compactness and the ability to express parallelism inherent to many streaming systems. In dataflow, a system is represented by a directed graph where nodes are called *actors* and edges are called *channels*. Actors represent computational kernels while channels typically capture data, control and resource dependencies between actors. The quanta of information exchanged across channels are called *tokens*. Actors involve themselves into communication with other actors by *firing*. The firing represents the quantum of computation during which actors consume tokens from their input channels and produce tokens in their output channels. Preconditions for firing are given by firing rules [32]. The numbers of tokens produced and consumed are called *rates*. In the timed versions of dataflow that we are investigating in this project, actor firings have duration that we call the actor *firing delay*.

There exist quite a number of dataflow models. They can be roughly divided into decidable [30] and dynamic dataflow models [18]. Decidable dataflow models can be considered versions of dataflow with restricted semantics so that the model can be scheduled at design-time as well as analysed for boundedness, deadlock and timing properties. Examples of decidable dataflow formalisms are synchronous dataflow (SDF) [5], cyclo-static dataflow [20] and scalable SDF [35]. Dynamic dataflow models offer more expressive power in exchange for a decrease in analysability and implementation efficiency [37]. Well-known examples are Boolean dataflow and dynamic dataflow [21].

All in all, in terms of support for design and analysis of timing-predictable and repeatable systems (and most predictable systems are at first *real-time systems*), among dataflow models, decidable dataflow models still play a more pronounced role than the echelons of emerging dynamic dataflow models. This in particular refers to SDF as the most stable and mature flavour of decidable dataflow that is characterized by its predictability, strong formal properties and amenability to powerful optimization techniques [18]. In SDF rates are fixed and known at compilation time. The firing rules of SDF are conjunctive [32] in the sense that for an actor to fire, every of its inbound channels must contain the number of tokens prescribed by the port rate defined by the actor and the inbound channel in consideration. Furthermore, they are distributive [32] in the sense that when the actor fires all outbound channels receive tokens in the quantity prescribed by the corresponding port rates. As we will further elaborate below, SDF graphs evolve in iterations. An iteration is a set of actor firings that have no net effect on the token distribution of the graph. The number of firings of a particular actor in an iteration is given in the so-called repetition vector of the graph. In this report, we consider the so-called self-timed execution of SDF graphs, which means that actors must fire as soon as they are enabled.

Several examples of use of SDF in design and analysis of predictable and repeatable systems can be found in [16][33][38]. If we study these papers, we see the SDF formalism is not only useful for reasoning about the functional behaviour and correctness of systems, but also, in its timed version [36], can be used when one needs to derive or prove worst-case performance guarantees, in particular throughput that is a vital performance indicator in real-time streaming systems, which is defined as the long-term average number of completed iterations per time-unit.

Many authors [9][26][28][29][36] have dealt with the problem of performance analysis of SDF models. To make these techniques applicable in everyday engineering practice, it is important that they are available in tools that can be utilized in fully or semi-automated design flows. The SDF<sup>3</sup> tool [4] developed by TU/e is such a tool. In particular, it implements various performance

analysis algorithms for dataflow MoCs such as synchronous dataflow (SDF) [5], cycle-static dataflow (CSDF) [6], and finite-state machine-based scenario-aware dataflow (FSM-SADF) [7].

The common characteristic of all of the algorithms is that they are in terms of performance adversely affected by the increase of repetition vector entries of the graph. In particular, the performance will scale at least linearly with the sum of the repetition vector entries [7].

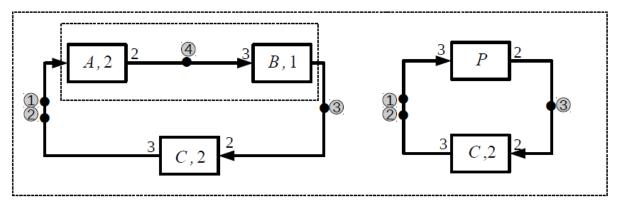

However, monolithic SDF models are inconvenient for capturing large designs. Therefore, allowing for compositional modelling is a necessity in the design of large systems as it enforces good engineering practices such as modularity and design reuse, and improves readability. Hierarchy has been introduced to SDF [39][17][34][24]. There is a technique for directly analyzing hierarchical SDF structures [23] but it is not exact, which means that it can only give a conservative throughput estimate but not the exact value. The *exact* throughput analysis algorithms existing so far can only be applied to hierarchical dataflow models after flattening them.

In this report, we propose a new exact modular technique for throughput analysis of a subclass of hierarchical SDF graphs with an arbitrary number of hierarchy levels that removes the need for flattening the graph. This is achieved by using (max,+)-based state-space representations of hierarchical actors instead of flattening in the context of existing throughput analysis techniques based on symbolic simulation. Furthermore, as our technique is able to take advantage of the hierarchical semantics of SDF, we argue that our technique helps to mitigate the adverse effect of an increase in the repetition vector entries on the performance of existing performance analysis techniques. This is due to the fact that no matter how many times a hierarchical actor is scheduled in the composition, we do not need to replicate the firings of all the actors embodied in the hierarchical actor as the existing techniques do, but only use its more compact state-space representation to capture the effects of its firing on the rest of the composition.

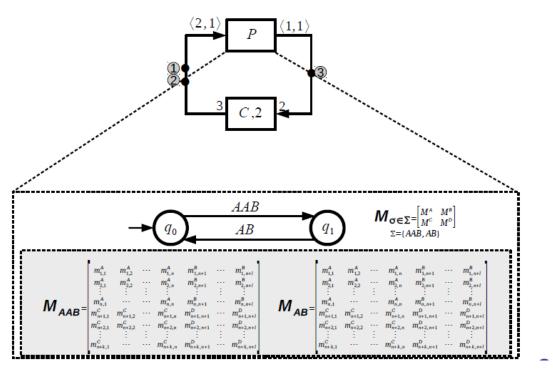

In addition (novelty compared to D5.1), we use our newly developed modular technique for throughput analysis of hierarchical SDF graphs to address the compositionality problem in SDF in the context of modular performance analysis and Deterministic SDF with Shared FIFOs.

In particular, hierarchical SDF models are not compositional: a composite SDF actor cannot be represented as an atomic SDF actor without loss of information that can lead to rate inconsistency or deadlock [57]. To remedy the former while working in the context of code generation, the authors of [57] propose a compositional abstraction of composite SDF actors called DSSF (Deterministic SDF with Shared FIFOs) that can be used for modular compilation. Nevertheless, the DSSF profiles have no accompanying performance models. In this work, we show how to incrementally build performance models for DSSF profiles using FSM-based scenario-aware dataflow (FSM-SADF) [60] across arbitrary levels of hierarchy that eventually brings us to the overall system performance model from which a performance metric can be derived using the usual (max,+)-based techniques. We illustrate our approach on a simple hierarchical SDF graph borrowed from [57].

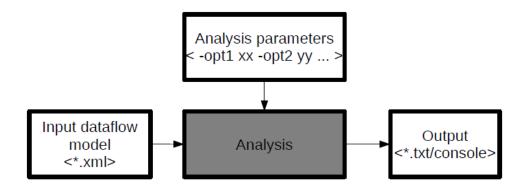

The remainder of Section 2.3 is organized as follows. Section 2.3.2 discusses related work, Section 2.3.3 covers the basic concepts used, Section 2.3.4 presents our throughput analysis technique, Section 2.3.5 compositionality, and Section 2.3.6 the analysis flow.

### 2.3.2. Related work

Roughly, state-of-the-art techniques for throughput analysis of SDF graphs can be divided in two groups.

The first group of approaches is based on the conversion of SDF graphs to equivalent homogeneous SDF (HSDF) graphs. HSDF is a special kind of SDF where all rates equal 1. The

basic algorithm for the conversion is described in [36]. The drawback of these approaches is that the size of the graph may expand exponentially [26]. However, advances have been made by the authors of [29] wherein the size of the expansion can be significantly reduced by constructing a so-called linear constraint graph (LCG) from the original SDF graph. With LCG in particular, the compaction is achieved by taking advantage of its redundancy and regularity. Still, some graphs as reported in [29] cannot be represented compactly by the LCG.

The second group of approaches are the simulation-based approaches. The seminal work of [28] performs explicit state-space exploration of the operational semantics of SDF. Despite its high worst-case complexity, the method works well in practice, while the techniques based on the conversion of [36] often fail. The symbolic simulation-based approach described in [26][9] uses (max,+) algebra to capture the self-timed execution of SDF graphs. In particular, the graph's evolution is sublimed into a simple recursive (max,+) linear matrix equation. The matrix in the equation is derived by symbolic simulation of one iteration of the SDF graph. This matrix can be considered as the incidence matrix of a weighted digraph, the maximum cycle mean of which is equal to the inverse of the graph's throughput.

All the exact techniques mentioned above have the common characteristic that the increase of the repetition vector entries in the graph will adversely affect their performance. In addition, the technique of [28] is also sensitive to the length of the graph's transient (self-timed execution of an SDF graph consists of a periodic phase preceded by a so-called transient phase). Furthermore, none of the exact techniques are directly applicable to hierarchical SDF structures, i.e., the hierarchical model should be flattened before.

There exists a technique that targets hierarchical SDF structures [23] but it is not exact, which means that it can only give a conservative throughput estimate but not the exact value.

### 2.3.3. Preliminaries

This section recaps the (max,+) algebra, the basic SDF concepts and the (max,+) linear system theoretic aspects of SDF that are used in this report.

# 2.3.3.1. (max,+) Algebra

Let  $\mathbb{R}_{max} = \mathbb{R} \cup \{-\infty\}$  where  $\mathbb{R}$  is the set of real numbers. For elements  $a, b \in \mathbb{R}_{max}$ , we define operations  $\oplus$  and  $\otimes$  with max as addition  $(a \oplus b \stackrel{\text{def}}{=} \max(a, b))$  and + as product  $(a \otimes b \stackrel{\text{def}}{=} a + b)$ . The set  $\mathbb{R}_{max}$  together with operations  $\oplus$  and  $\otimes$  extended to matrices and vectors in the same way as in conventional linear algebra is called  $(\max, +)$  algebra. The set of *n*-dimensional  $(\max, +)$ vectors is denoted  $\mathbb{R}_{max}^n$ , while  $\mathbb{R}_{max}^{n \times n}$  denotes the set of  $n \times n$   $(\max, +)$  matrices. The (sup-) sum of matrices  $A, B \in \mathbb{R}_{max}^{n \times n}$  is defined by  $[A \oplus B]_{i,j} = [A]_{i,j} \oplus [B]_{i,j}$  where  $[A]_{i,j}$  and  $[B]_{i,j}$  are entries of matrices A and B with indices i and j. The matrix product  $A \otimes B$  is defined by  $[A \otimes B]_{i,j} = \oplus_{k=1}^n [A]_{i,k} \otimes [B]_{k,i}$ .

### 2.3.3.2. Synchronous dataflow

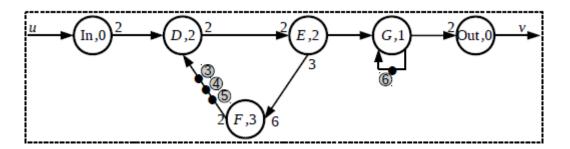

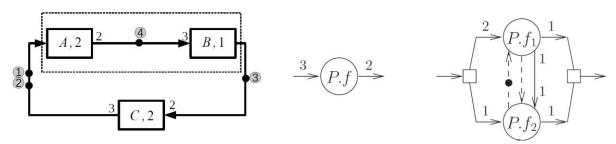

Figure 10 shows an SDF graph.

Figure 10: Example of an SDF graph.

The graph has six actors, In, D, E, F, G and Out. Actor firing delays are denoted next to actor names. Rates are denoted next to channel ends with a convention that the omission of a rate value implies the value of 1. Notice that the graph in the figure has two feedback loops, one going from actor E to D across F, and a so-called self-edge from actor G back to itself. Such feedback loops can cause the graph to deadlock because actors in the loops depend on each other for tokens. Therefore, feedback loops must include a certain number of *initial tokens* that specify the initial condition from which the execution starts. In the figure, these are depicted using grey circles and are marked as 3, 4, 5, 6.

SDF graphs evolve in iterations. An iteration is a set of actor firings that have no net effect on the token distribution in the graph. The numbers of firings are stored in the repetition vector of the graph  $\Gamma$ . For the graph in Figure 10,  $\Gamma(In, D, E, F, G, Out) = [1, 2, 2, 1, 2, 1]^T$ . This vector can be obtained by solving the so-called set of balance equations for an SDF graph [5]. Notice that iterations can overlap in time, i.e. they can be pipelined. An SDF graph can be closed or open [39] depending on whether all input ports are connected or not, respectively. The graph in Figure 10 is open as not all its input ports are connected.

# 2.3.3.3. (max,+) Semantics of Synchronous Dataflow

We use (max,+) algebra [15] to model timed SDF graphs. It is a natural choice as it has two operations that determine the self-timed execution of SDF graphs: synchronization and delay. Synchronization manifests itself when an actor waits for all its input tokens to become available ( $\oplus$  i.e. max in (max,+)) before firing. The delay manifests itself in the fact that tokens will be produced only after an amount of time corresponding to the actor firing delay after the firing has begun ( $\otimes$  i.e. + in (max,+)). We mentioned that SDF graphs evolve in iterations that restore the graph back to its initial state. The initial state is determined by the distribution of initial tokens over the channels of the graph. Thus, in terms of time, the evolution of an SDF graph can be represented as a sequence of vectors x(k) where each entry of the vector stores the availability time of a token produced in place of a particular initial token after the *k*-th iteration of the graph. Geilen [9] shows that this sequence (for closed SDF graphs) can be determined by a (max,+) linear recursive equation

$$\boldsymbol{x}(k+1) = \boldsymbol{M} \otimes \boldsymbol{x}(k), \tag{1.1.1}$$

where *M* is the (max,+) matrix of the graph that defines its state-space representation. For open SDF graphs, whose inputs are fed by the token sequence u(k), and that produce tokens the timestamps of which are stored in sequence v(k), (1.1.1) can be generalized to the form

$$\begin{bmatrix} x(k+1) \\ v(k) \end{bmatrix} = \begin{bmatrix} M^A & M^B \\ M^C & M^D \end{bmatrix} \otimes \begin{bmatrix} x(k) \\ u(k) \end{bmatrix}$$

(1.1.2)

where  $M^A$  is the state matrix,  $M^B$  is the input matrix,  $M^C$  is the output matrix and  $M^D$  is the feed-through matrix [27].

These matrices (as in conventional linear system theory) encode mutual dependencies between inputs, outputs and internal state. They can be derived via symbolic simulation of one iteration of the graph as described in [9]. We illustrate how to do this on the example SDF graph in Figure 10. To establish the relationship between the timestamps of tokens contained in (1.1.2) we need to express the timestamps of tokens produced in positions of initial tokens after the (k+1)-st iteration and tokens produced at the outputs of the graph as (max,+) linear combinations of the timestamps of the same tokens after the k-th graph iteration and the input tokens. For the graph of Figure 10,

$$t_3 = \begin{bmatrix} 0 & -\infty & -\infty & -\infty \end{bmatrix} \otimes \begin{bmatrix} x(k) & u(k) \end{bmatrix}^T, \ t_4 = \begin{bmatrix} -\infty & 0 & -\infty & -\infty \end{bmatrix} \otimes \begin{bmatrix} x(k) & u(k) \end{bmatrix}^T$$

all the way up to  $t_u = \begin{bmatrix} -\infty & -\infty & -\infty & 0 \end{bmatrix} \otimes \begin{bmatrix} x(k) & u(k) \end{bmatrix}^T$ . We call these timestamps symbolic timestamps. We now perform symbolic simulation. The iteration is given by the schedule  $In D^2 E^2 F G^2 Out$  where powers represent actor repetition counts. The iteration starts by actor *In* firing. This firing consumes the input token *u* and produces two tokens in channel (*In*, *D*) carrying the symbolic timestamp  $t_u \otimes 0 = \begin{bmatrix} -\infty & -\infty & -\infty & 0 \end{bmatrix}$ . These tokens along with initial tokens in channel (*F*, *D*) fuel two firings of actor *D* as follows. The firings produce two tokens each. The first two have the symbolic timestamp

$$([-\infty -\infty -\infty -\infty 0] \oplus t_3) \otimes 2 = [2 -\infty -\infty -\infty 2]$$

The remaining are of the following symbolic timestamp

$$(\begin{bmatrix} -\infty & -\infty & -\infty & 0 \end{bmatrix} \oplus t_4) \otimes 2 = \begin{bmatrix} -\infty & 2 & -\infty & -\infty & 2 \end{bmatrix}$$

Then we proceed with actor E the first firing of which is initialized by the tokens produced by the first firing of actor D. The firing results in production of three tokens in channel (E, F) and one token in channel (*E*, *G*) with the timestamp  $\begin{bmatrix} 2 & -\infty & -\infty & 2 \end{bmatrix} \otimes 2 = \begin{bmatrix} 4 & -\infty & -\infty & 4 \end{bmatrix}$ . produced by the second firing are The tokens available at  $\begin{bmatrix} -\infty & 2 & -\infty & -\infty & 2 \end{bmatrix} \otimes 2 = \begin{bmatrix} -\infty & 4 & -\infty & -\infty & 4 \end{bmatrix}$ . This enables actor *F* to fire and restore tokens in position 4 and 5 with the symbolic timestamps  $t_4' = t_5' = \begin{bmatrix} 7 & 7 & -\infty & -\infty & 7 \end{bmatrix}$ . Note that token 5 was not consumed in the current iteration but was shifted in position of token 3. Thus,  $t_3' = t_5 = \begin{bmatrix} -\infty & -\infty & 0 & -\infty \end{bmatrix}$ . Similarly, actor *G* fires and its second firing results in restoring the token in position 6 that ends up with the timestamp  $t_6' = \begin{bmatrix} 6 & 5 & -\infty & 2 & 6 \end{bmatrix}$ . This is also the timestamp of the token produced on the output, i.e.  $t_v = t_6'$ . If we gather the symbolic

timestamps  $t'_{3}, t'_{4}, t'_{5}, t'_{6}$  and  $t'_{v}$  row-by-row into a matrix, we obtain

$$\begin{bmatrix} x(k+1) \\ v(k) \end{bmatrix} = \begin{bmatrix} -\infty & -\infty & 0 & -\infty \\ 7 & 7 & -\infty & -\infty \\ 7 & 7 & -\infty & -\infty \\ 6 & 5 & -\infty & 2 \\ \hline 6 & 5 & -\infty & 2 \\ \hline 6 & 5 & -\infty & 2 \\ \hline 6 & 5 & -\infty & 2 \\ \hline 6 & 5 & -\infty & 2 \\ \hline 6 & 5 & -\infty & 2 \\ \hline 6 & 5 & -\infty & 2 \\ \hline 6 & 5 & -\infty & 2 \\ \hline 6 & 5 & -\infty & 2 \\ \hline 6 & 5 & -\infty & 2 \\ \hline 6 & 5 & -\infty & 2 \\ \hline 6 & 5 & -\infty & 2 \\ \hline 6 & 5 & -\infty & 2 \\ \hline 6 & 5 & -\infty & 2 \\ \hline 6 & 5 & -\infty & 2 \\ \hline 6 & 5 & -\infty & 2 \\ \hline 6 & 5 & -\infty & 2 \\ \hline 6 & 5 & -\infty & 2 \\ \hline 6 & 5 & -\infty & 2 \\ \hline 6 & 5 & -\infty & 2 \\ \hline 6 & 5 & -\infty & 2 \\ \hline 6 & 5 & -\infty & 2 \\ \hline 6 & 5 & -\infty & 2 \\ \hline 6 & 5 & -\infty & 2 \\ \hline 6 & 5 & -\infty & 2 \\ \hline 6 & 5 & -\infty & 2 \\ \hline 6 & 5 & -\infty & 2 \\ \hline 6 & 5 & -\infty & 2 \\ \hline 6 & 5 & -\infty & 2 \\ \hline 6 & 5 & -\infty & 2 \\ \hline 6 & 5 & -\infty & 2 \\ \hline 6 & 5 & -\infty & 2 \\ \hline 6 & 5 & -\infty & 2 \\ \hline 7 & 7 \\ 7 \\ 6 \\ 1 & 1.3 \\ \hline 7 \\ 1 & 1.3 \\ 1 & 1.3 \\ \hline 7 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ \hline 7 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1 & 1.3 \\ 1$$

where  $x(k+1) = \begin{bmatrix} t_3' & t_4' & t_5' & t_6' \end{bmatrix}^T$ ,  $v(k) = \begin{bmatrix} t_v \end{bmatrix}^T$ ,  $x(k) = \begin{bmatrix} t_3 & t_4 & t_5 & t_6 \end{bmatrix}^T$  and  $u(k) = \begin{bmatrix} t_u \end{bmatrix}^T$ .

## 2.3.3.4. Hierarchy in SDF Graphs

In this report, following the terminology of [39], when we talk about hierarchical SDF graphs, we mean graphs that contain hierarchical actors. Unlike atomic actors, a hierarchical actor encapsulates an SDF graph. Hierarchical actors can then be connected to other SDF actors, either atomic or hierarchical to form hierarchies of arbitrary depths.

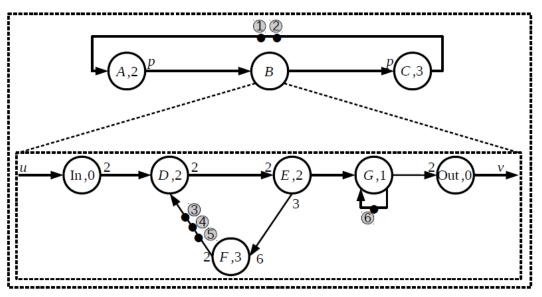

An example of a hierarchical SDF graph is shown in Figure 11.

Figure 11: Example of a hierarchical SDF graph.

In the figure, the top-level graph is composed out of three actors A, B and C. Actors A and C are atomic, while actor B is a hierarchical actor that encapsulates the SDF graph of Figure 10. In this particular example, the output port of actor A is connected to the input port of actor In, while the input port of actor C is connected to the output port of actor *Out* of the encapsulated graph of hierarchical actor B.

Although hierarchical SDF models are widely used (e.g. in the well-known Ptolemy II framework [25]), care must be taken as there is one complication. In general, hierarchical SDF models are not compositional. In particular, a hierarchical SDF actor cannot be represented by an atomic SDF actor without loss of information that can lead to inconsistency and deadlock [39]. In this report, we assume that only valid aggregations are specified.

# 2.3.3.5. FSM-based Scenario-Aware Dataflow (FSM-SADF)

FSM-SADF is a dynamic dataflow model that preserves as much as possible of the determinacy of dataflow behaviour while introducing the possibility of non-deterministic variations in the form of scenarios individually represented as SDF graphs. Operationally, an FSM-SADF evolves in (possibly) partial iterations of its non-deterministically selected scenarios captured by SDF graphs. The scenario FSM defines the scenario occurrence patterns.

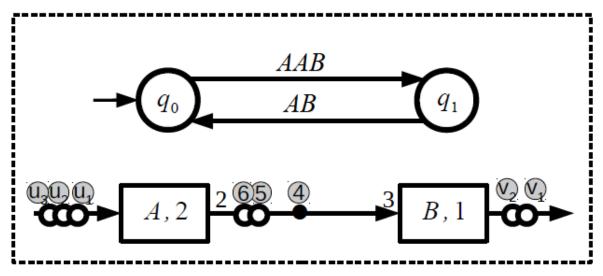

Figure 12 shows an example of an FSM-SADF graph.

Figure 12: An FSM-SADF graph

The scenario FSM is shown in the upper part of the figure while the associated scenario graphs are shown in the lower part of the figure. The FSM-SADF has two scenarios: "*AAB*" and "*AB*" specifying the orderings of actor firings in the associated scenario graph. With the FSM as shown, the scenario traces generated by the model are as follows: ("*AAB*" "*AB*")\*. In the general case, from one scenario to the other, the set of firing actors, their port rates and firing delays will differ. The entailing (max,+) scenario representations and the control specification (the FSM of the FSM-SADF) are used to perform the worst-case performance analysis of the model based on the (max,+)-linear switched system semantics of FSM-SADF involving a structure called the (max,+)-automaton [58]. For details we refer to [59] and [60].

### 2.3.4. Throughput Analysis of Hierarchical SDF Models

In this section, we discuss throughput analysis for a class of hierarchical SDF models where starting from the bottom level of the hierarchy, the firing of every hierarchical actor implies the execution of one full iteration of the encapsulated graph. In particular, we propose a technique that is an enhancement of the symbolic simulation procedure of [9] that is able to take advantage of the SDF hierarchy semantics.

Our technique combines symbolic simulation and the system-theoretic view on SDF graphs as (max,+) linear systems that recognize the "usual" state-space representation based on the state, input, output and feedthrough matrices (cf. (1.1.2)).

## 2.3.4.1. Our algorithm

A high-level overview of our algorithm is the following Algorithm 1.

| Algorithm 1: Throughput analysis for hierarchical SDF models.         |  |

|-----------------------------------------------------------------------|--|

| input : A hierarchical SDF graph $G$<br>output: Throughput Thr of $G$ |  |

| 1 $H = $ IsolateHierarchyLevels( $G$ )                                |  |

| <b>2</b> for each hierarchy level $h$ in $H$ do                       |  |

| 3 for each hierarchical actor a in h do                               |  |

| 4 $M = SymbolicSimulation+(a, S[h-1][:])$                             |  |

| $5 \qquad S[h][a] = M$                                                |  |

| 6 end                                                                 |  |

| 7 end                                                                 |  |

| 8 $Cg = \text{CommunicationGraph}(M)$                                 |  |

| 9 $Thr = 1/MCM(Cg)$                                                   |  |

Algorithm 1: Throughput analysis for hierarchical SDF models

The input to the algorithm is a hierarchical SDF graph G, while the output of the algorithm is the throughput Thr of the graph. We begin the procedure by isolating the hierarchy levels of the graph starting in a bottom-up manner (cf. Line 1). This can be done by employing a suitable variant of the reverse breadth-first search algorithm. Thereafter for each hierarchical actor (cf. Line 3) at the current hierarchy level (cf. Line 4) we perform symbolic simulation in order to obtain the relevant state-space representation of the hierarchical actor (cf. Line 2). The representation (composite matrix that includes the state, input, output and feedthrough submatrices) is stored because later on the symbolic simulation at a higher hierarchy level will need this representation (note that the symbolic simulation in Line 4 is invoked with all the state-space representations belonging to the previous hierarchy level). Finally, when we reach the highest hierarchy level, the symbolic simulation will produce a state-space representation of G for which we construct the corresponding communication graph (cf. Line 8). For details on how to construct the communication graph of a (max,+) matrix we refer the interested reader to [31]. The throughput of the graph equals the inverse of the maximum cycle mean of the communication graph (cf. Line 9). Note that the algorithm assumes the existence of a hierarchy in the sense that a graph composed only of atomic actors is assumed to be a hierarchical graph composed of one hierarchical actor that encapsulates the atomic actor composition.

### 2.3.4.2. Symbolic Simulation

Algorithm 1 as its core part uses symbolic simulation. The symbolic simulation as originally proposed by [9] cannot take advantage of semantics of hierarchical SDF models.

This means that if we are to use the techniques of [9] to compute the throughput of a hierarchical SDF model, we first need to flatten the hierarchy, i.e. to transform the graph to one without it.

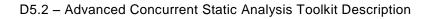

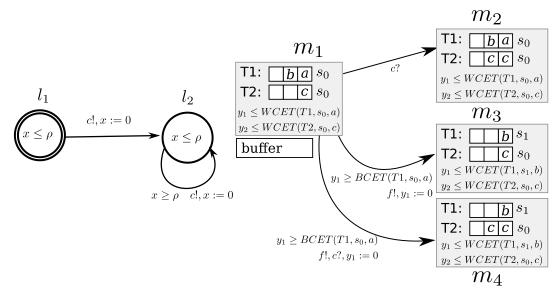

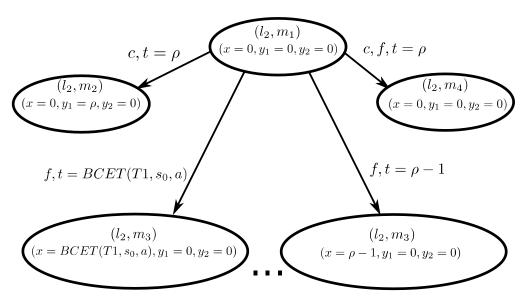

As explained in Section 2.3.3.3, symbolic simulation derives the state-space representation of an SDF graph by simulating the graph for exactly one iteration following the iteration schedule. In the schedule, every actor is fired the number of times corresponding to the repetition vector entry for that actor. The procedure requires administration of every token produced and consumed during the iteration. Thus, for graphs with large repetition vector entries, the symbolic simulation can become a bottleneck in the overall throughput analysis flow. In case of hierarchical SDF models (regardless whether the hierarchy is extracted from a flat graph or comes in the