(ITEA 3 – 17003)

PANORAMA Boosting Design Efficiency for Heterogeneous<sup>3</sup> Systems

Deliverable: D6.5

Design Handbook

Work Package: 6 Design Flow and Traceability

Task: T6.5 Integrated Safety Analysis

**Document Type: Document Version**: Document Preparation Date: 2022-03-31

Deliverable Final

Classification: Public Contract Start Date: 2019-04-01 Duration: 2022-03-31

# Authors

Karsten Albers Inchron GmbH Mahmoud Bazzal Dortmund University of Applied Sciences and Arts Jan Steffen Becker OFFIS e.V. Maria Bonner Siemens AG Daniel Fruhner Dortmund University of Applied Sciences and Arts Björn Koopmann OFFIS e.V. Olexiy Kupriyanov Siemens AG Harald Mackamul Robert Bosch GmbH Philip Okonkwo Dortmund University of Applied Sciences and Arts David Schmelter Fraunhofer IEM Jan-Philipp Steghöfer University of Gothenburg Ingo Stierand OFFIS e.V. Marc Zeller Siemens AG

# Contents

| Αι | uthors                     | 3                                                                  | ii                 |

|----|----------------------------|--------------------------------------------------------------------|--------------------|

| Su | ımma                       | ry                                                                 | vii                |

| 1  | <b>Intro</b><br>1.1<br>1.2 | Deduction<br>Scope and Objectives                                  | <b>1</b><br>1<br>2 |

| 2  | Bac                        | kground                                                            | 3                  |

|    | $2.1 \\ 2.2 \\ 2.3$        | Existing Design Processes as described in Deliverable 6.1          | $3 \\ 5 \\ 6$      |

| 3  | Met                        | hodology                                                           | 8                  |

|    | 3.1                        | Focus Group for Process Definition                                 | 8                  |

|    | 3.2                        | Focus Group on Collaboration                                       | 9                  |

|    | 3.3                        | Survey                                                             | 9                  |

|    | 3.4                        | Continuous Refinement                                              | 9                  |

|    | 3.5                        | Creation of Engineering Scenarios                                  | 10                 |

|    | 3.6                        | Analysis of Engineering Scenarios                                  | 11                 |

| 4  | Desi                       | gn Process                                                         | 12                 |

|    | 4.1                        | Approach and Overview                                              | 12                 |

|    | 4.2                        | Design Phases                                                      | 14                 |

|    |                            | 4.2.1 System Analysis                                              | 14                 |

|    |                            | 4.2.2 System Safety Design                                         | 16                 |

|    |                            | 4.2.3 Assessment and Optimization                                  | 18                 |

| 5  | Engi                       | ineering Scenarios                                                 | 20                 |

|    | 5.1                        | Change Impact Analysis (ES-1)                                      | 21                 |

|    | 5.2                        | Enhanced Project Development Life Cycle (ES-2)                     | 25                 |

|    | 5.3                        | Verification of Consistency and Timing of End-to-End Chains (ES-3) | 29                 |

|    | 5.4                        | Early Design Space Exploration (ES-4)                              | 31                 |

|    | 5.5                        | Optimization of Task Deployment (ES-5)                             | 33                 |

|    | 5.6                        | Verification of End-to-End Latency Requirements (ES-6)             | 36                 |

|    | 5.7                        | Analysis of Timing Behavior (ES-7)                                 | 39                 |

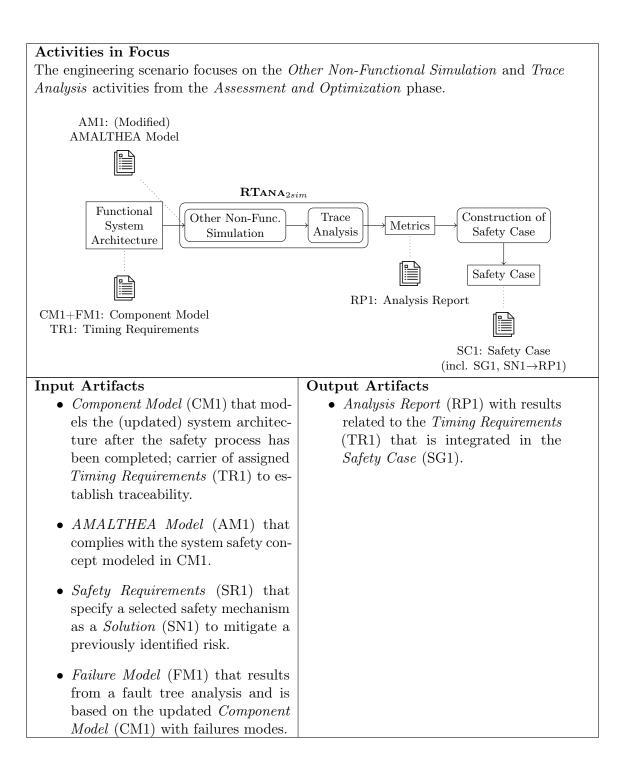

|    | 5.8                        | Correct Implementation of Safety Mechanisms (ES-8)                 | 41                 |

|    | 5.9                        | Fault-Tolerant Scheduling Analysis (ES-9)                          | 45                 |

| 7 | Conclusion                                      | 63 |

|---|-------------------------------------------------|----|

|   | 6.3 Summary                                     | 62 |

|   | 6.2 Synthesis                                   | 59 |

|   | 6.1 Coverage Analysis                           | 55 |

| 6 | Discussion                                      | 55 |

|   | 5.13 Other Tools                                | 54 |

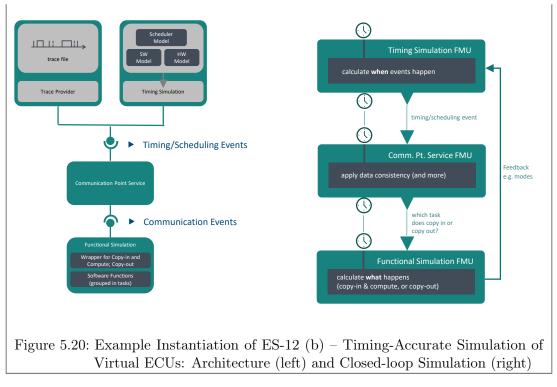

|   | 5.12 SystemC Performance Simulation (ES-12)     | 51 |

|   | 5.11 Trace Analysis for Timing Behavior (ES-11) | 49 |

|   | 5.10 Simulation of Timing Behavior (ES-10)      | 47 |

|   |                                                 |    |

# List of Figures

| 4.1  | 0 0                                                   | 13 |

|------|-------------------------------------------------------|----|

| 4.2  | System Analysis (Phase 1)                             | 15 |

| 4.3  |                                                       | 16 |

| 4.4  | Assessment and Optimization (Phase 3)                 | 18 |

| 5.1  | Traceability Information Used in ES-1                 | 23 |

| 5.2  | Example Instantiation 1 of ES-1                       | 24 |

| 5.3  | Example Instantiation 2 of ES-1                       | 24 |

| 5.4  | Example Instantiation of ES-2 (a)                     | 26 |

| 5.5  | Example Instantiation of ES-2 (b)                     | 27 |

| 5.6  | Example Instantiation of ES-2 (c)                     | 27 |

| 5.7  | Example Instantiation of ES-2 (d)                     | 28 |

| 5.8  | Example Instantiation of ES-4                         | 32 |

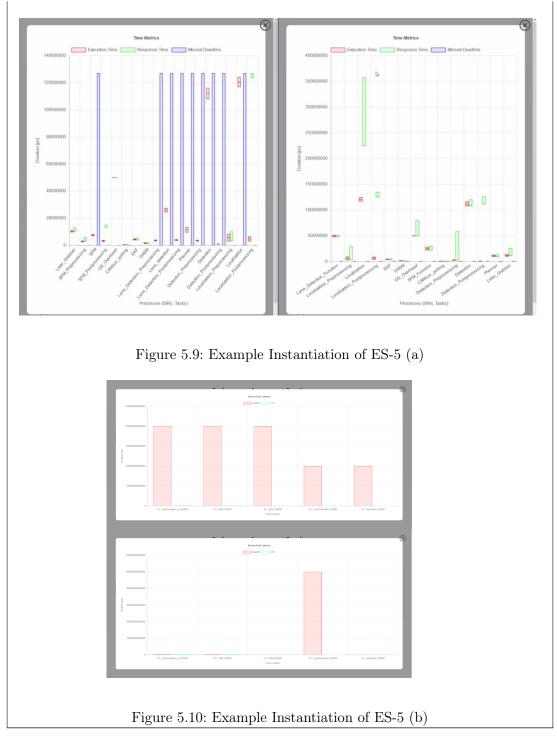

| 5.9  | Example Instantiation of ES-5 (a)                     | 35 |

| 5.10 | Example Instantiation of ES-5 (b)                     | 35 |

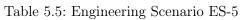

| 5.11 | Example Instantiation of ES-6 (a)                     | 37 |

| 5.12 | Example Instantiation of ES-6 (b)                     | 37 |

| 5.13 | Example Instantiation of ES-6 (c)                     | 37 |

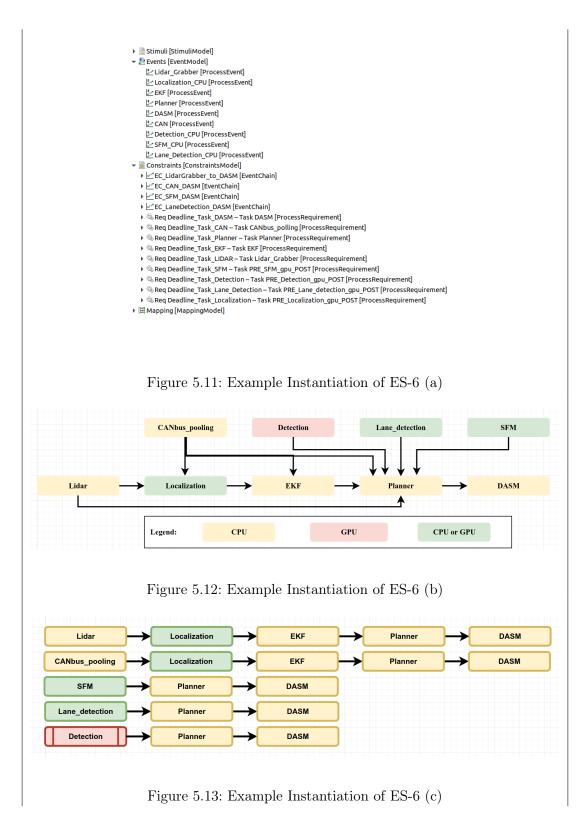

| 5.14 | Example Instantiation of ES-6 (d)                     | 38 |

| 5.15 | Structure of ES-8                                     | 11 |

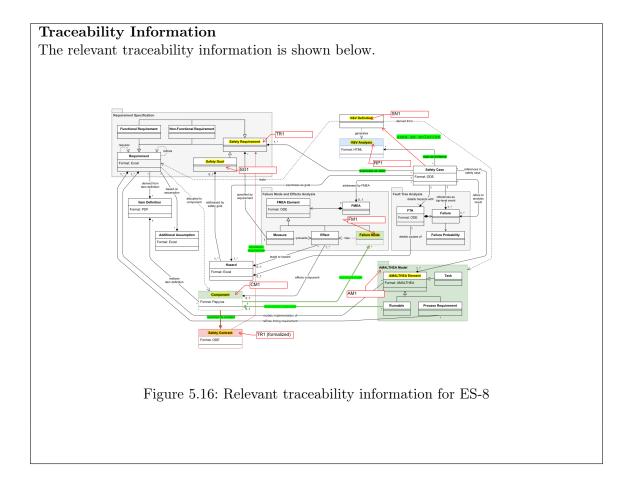

| 5.16 | Relevant traceability information for ES-8            | 43 |

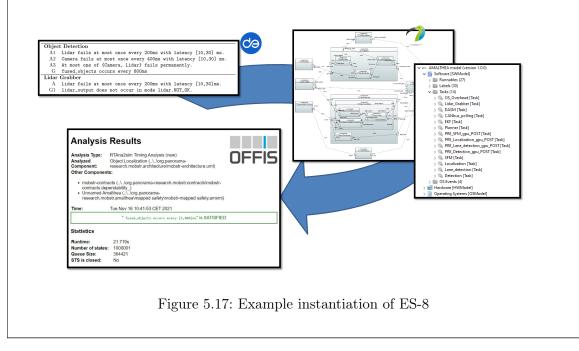

| 5.17 | Example instantiation of ES-8                         | 14 |

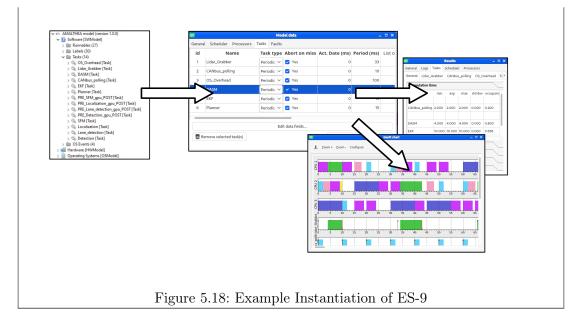

| 5.18 | Example Instantiation of ES-9                         | 46 |

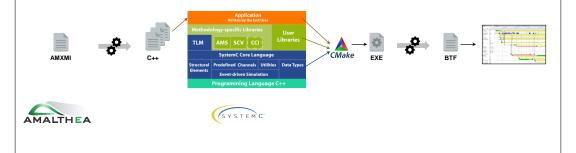

| 5.19 | Example Instantiation of ES-12 (a)                    | 53 |

|      |                                                       | 54 |

| 6.1  | Design Steps Coverage                                 | 56 |

| 6.2  | Identified clusters and exchange formats between them | 51 |

# List of Tables

| 3.1  | Template for the Collection of the Engineering Scenarios | 10 |

|------|----------------------------------------------------------|----|

| 5.1  | Engineering Scenario ES-1                                | 24 |

| 5.2  | Engineering Scenario ES-2                                | 28 |

| 5.3  |                                                          | 30 |

| 5.4  |                                                          | 32 |

| 5.5  |                                                          | 35 |

| 5.6  |                                                          | 38 |

| 5.7  | Engineering Scenario ES-7                                | 40 |

| 5.8  | Engineering Scenario ES-8                                | 44 |

| 5.9  | Engineering Scenario ES-9                                | 46 |

| 5.10 | Engineering Scenario ES-10                               | 48 |

| 5.11 | Engineering Scenario ES-11                               | 50 |

| 5.12 | Engineering Scenario ES-12                               | 54 |

| 6.1  | Coverage of ISO 26262 Work Products                      | 57 |

| 6.2  |                                                          | 60 |

| 6.3  | Non-Agreed Formats (Not Exhaustive)                      | 60 |

| 6.4  | Activity Clusters for Hardware/Software-Level Design     |    |

## Summary

This document describes a design process for the development of heterogeneous, safetycritical systems as considered in the PANORAMA project. The process has been defined as a flow of activities and the work products that provide the interfaces between activities. It is divided into three phase, namely *System Analysis*, *System Safety Design*, and *Assessment and Optimization*, to which the activities are assigned.

Many aspects must be considered beyond a simple structural view for instantiating such a design process. The document gives an overview of the aspects that played an important role in the development of the process, among which are collaboration and requirements imposed by existing safety standards. Particularly, the safety aspect is an important driving factor for the development of the process. The activities are aligned with the ISO 26262 standard, and a coverage analysis with the corresponding mandatory clauses in the ISO standard is performed.

The document discusses a total of 12 engineering scenarios, which have been implemented by the project partners and fit into the process structure. They exemplify the instantiation of parts of the process and thus contribute to demonstrating its applicability. Finally, an analysis is performed on the results in order to assess the actual coverage of the process with respect to the engineering scenarios as well as the completeness and consistency of the interfaces between these scenarios. Finally, a gap analysis is conducted in order to identify open challenges and to set the stage for future activities.

# 1 Introduction

Software developers in the automotive and avionics industries are exposed to foundational changes in how systems are architected and developed. Most importantly, electrical architectures in vehicles and aircraft have become highly networked and increasingly include specialized and networked hardware, such as AI accelerators for deep learning in autonomous vehicles. Centralized hardware platforms are complemented with specialized hardware and software for functions such as drive, comfort, and multimedia. At the same time, collaboration between partners along the value chain becomes more important as software providers, domain experts, and service providers will become more involved in future development processes.

The increased heterogeneity on all these levels may, however, not impede the safety of the system. On the contrary ensuring safety becomes even more important in systems that include learning components and that make autonomous decisions in situations that are impossible to fully predict at run-time [GJW+20]. Safety standards are adopted in all relevant domains (e.g., ISO 26262 [Int18] for automotive, ISO 17894 [Int05] for maritime, and ARP 4754/61 [Soc96] for avionics).

In the light of these changes and challenges, the automotive and avionics industries are changing their methods, tools, platforms, and their *development processes* (see, e.g., [SKHW19; HWS17]). Collaboration during development and close cooperation between OEMs and suppliers will become the norm. An agile mindset, which has transformed OEMs in the past years, is increasingly applied to suppliers as well [HMSS16]. Instead of treating suppliers and the components they deliver as black boxes, they become increasingly integrated into the development process and requirements and systems adapt during development. Suppliers thus work more closely with the product teams, but need to show more flexibility as they track the product development. Continuous safety engineering also requires them to continuously provide analysis result and participate in the ongoing safety argumentation (see, e.g., [BL21]).

### 1.1 Scope and Objectives

This design handbook intends to showcase how the results of the PANORAMA project can be integrated into a development process that supports the design of safety-critical systems in the light of the challenges outlined above. To address this emerging new development paradigm, this report answers the following research questions:

**RQ-1** What must a system engineering process look like to enable the standard-compliant development of heterogeneous systems?

- RQ-2 What are typical engineering scenarios? How does the process support these scenarios?

- **RQ-3** Which tools can be used to implement the process? How can tool interoperability be ensured along the process?

- **RQ-4** How can applicability of the process be ensured?

We have formulated these research questions based on the needs of a number of partners from the avionics and automotive industry who participated in PANORAMA. These organizations are working towards integrating suppliers and OEMs more closely in the development processes, increasing the complexity of the systems under construction, reducing the time to market, and delivering safe and reliable products.

By answering these questions, we provide the following contributions:

- **Design Process** We investigate which activities and work products are relevant for such a process and which commonalities the different standards prescribe (cf. Chapter 4).

- **Engineering Scenarios** Engineering scenarios describe typical sub-processes engineers of safety-critical systems conduct. We identify such scenarios and show how the process we designed supports them (cf. Chapter 5).

- **Tool Support** We identify commonly used tools that support the different activities of the design process and show how standardized interchange formats can be used to enable exchange of information between the relevant stakeholders in the process (cf. Chapter 6).

- Analysis of Engineering Scenarios We analyze the engineering scenarios in terms of which aspects of the relevant standards they cover, which patterns they include that can be reused in other contexts, etc. Overall, this provides insights into the applicability of the design process and the generalizability of our findings (cf. Chapter 6).

#### 1.2 Outline

The document is structured as follows: In Chapter 2, we introduce the relevant background, including safety standards and collaboration approaches. We describe the methodology we followed to arrive at our results in Chapter 3. Based on this, we showcase the design process in Chapter 4 and detail the activities, work products, tools, and domain-specific languages that are relevant for it. Engineering scenarios are then introduced in Chapter 5 before their analysis is discussed in the context of the design process in Chapter 6. Chapter 7 concludes the report.

# 2 Background

The definition of an applicable design process, with its phases and steps, their interfaces and (intermediate) work products depends on numerous factors, such as effective regulations for the intended work products, infrastructure and organizational structure, as well as existing tools, best practices and legacy support. One of the main objectives of the PANORAMA project is to establish a design flow that:

- enables covering the engineering challenges the project is aiming at in industryrelevant setups (cf. Chapter 1); and that

- can be instantiated with the methods and tools developed in the project for a representative set of engineering scenarios.

To this end, we documented the relevant state of practice as well as requirements from the industrial partners for such a process in Deliverable 6.1 [MCA+20]. The findings of this deliverable are summarized in Section 2.1. In addition, we discuss the role of different safety standards on the definition of the design process in Section 2.2 and the influence on collaboration between different organizations in Section 2.3.

#### 2.1 Existing Design Processes as described in Deliverable 6.1

We collected the *state-of-the-art of collaborative development processes* by conducting a literature review and a review of results from previous projects, in particular projects with strong industrial focus such as AMALTHEA4public, ARAMiS II, and DEIS. In AMALTHEA4public, e.g., first attempts have been made to map out a generic design process and show which activities and tools can be used to achieve certain objectives defined in ISO 26262 [TMSP16]. We also considered how collaboration can be achieved from a tooling perspective, e.g., by considering version control systems and real-time collaboration tools.

One of the outcomes of the ARAMiS II project was a design process that is designed to be applicable in many domains and aligned with different safety standards. Likewise, Siemens has already described a collaboration workflow for use with their Polarion platform. These processes are not complete in the sense that they cover the entire development life-cycle. For instance, timing and safety analysis activities are not featured prominently in either.

One important focus of both the AMALTHEA4public and the DEIS project was interchange of information. In AMALTHEA4public, the AMALTHEA model has been defined as a way to exchange information about system design, timing, hardware, and other aspects. In DEIS, the Open Dependability Exchange (ODE) model has been defined as a way to exchange information about safety and reliability concerns. Both models have been taken up and refined in PANORAMA and form an important foundation of information exchange. Any collaborative design process needs to ensure that information can be exchanged freely and can be understood, analyzed, and created by the involved parties.

To define the *state-of-practice of collaborative development processes*, we collected use case descriptions from the industrial partners that contained typical collaboration scenarios during a typical endeavor, ran an ideation workshop to collect ideas and requirements for improved collaboration, and held a focus group to understand these scenarios and their challenges better. The results are structured along different dimensions of the daily practice:

- **Collaboration Workflows** change during the project duration and differ in intensity according to the current phase. Depending on the relationship between partners, different contractual solutions are used and long-term relationships between partners can decrease formality of the arrangements.

- Artifact Exchange is of vital importance for the success of the endeavor. The level of formality of the artifacts changes over the course of the endeavor with less formal requirements exchanged in the beginning and more formal and structured artifacts such as Matlab/Simulink models exchanged later on. In any case, it is important that file formats are standardized and tool providers are included in the process of defining standards for the artifacts.

- **Infrastructure** to process these artifacts also need to be set up and integrated into other tools such as application life-cycle management tools or issue tracking tools.

- **Traceability** between the individual work artifacts needs to be established, especially if they are updated frequently by different parties. Clearly established and maintained traceability links support, among other things, change impact analysis and allow for the easy and (semi-)automatic creation of reports that are required for certification purposes.

- Security and Intellectual Property Management needs to be taken into consideration whenever IP needs to be protected. When different partners collaborate and exchange information, some of it might be sensitive and should, e.g., be prevented from introspection by unauthorized parties.

Based on these findings, we established a number of *requirements for future collaborative development processes.* The two main sources of requirements are the ISO 26262 safety standard used for the development of vehicles and the ideation workshop mentioned above. While the full list of requirements can be found in [MCA+20], it is worth noting that these two sources provided requirements on the process itself, the models that are exchanged, the verification and validation tools that are used, and the way knowledge is managed.

The final step described in Deliverable 6.1 is a *gap analysis* between these requirements and state of the art and practice. Noteworthy gaps are:

- there is a need to create and maintain safety cases in form of models;

- there is a need to capture design decisions explicitly in the model itself;

- there is a need for a standardized tool environment with tools flexible enough to support different concrete projects; with standardized exchange formats for the most common artifacts; and with extensibility to address customer-specific requests;

- there is a need to use trace information for program comprehension or to maintain an overview of the system;

- there is a need to link analysis results to quality attributes that can be improved in the model;

- there is a need to have a standard process in-house and have a way to synchronize this standard process with each supplier;

PANORAMA provide solutions for a number of these gaps. Not all of these solutions are addressed in this deliverable, but deliverables from other work packages cover, e.g., the creation of safety analysis artifacts needed for model-based safety cases. This deliverable will focus on process aspects and, in particular, will focus on how a generic process description supports a number of engineering scenarios based on standardized tooling and common exchange formats.

## 2.2 The Role of ISO 26262 in the Definition of the Design Process

For systems where functional correctness and safety is of high importance, there exist standards such as IEC 61508 [Int98], which provide guidance on how to address the safety-related aspects in the development process such as the assessment of risks, derivation of safety requirements and adequate design steps to assure that the developed system fulfills these requirements. It was adopted in different domain specific standards like ISO 26262 (automotive) [Int18], ISO 17894 (maritime) [Int05] and ARP 4754/61 (avionics) [Soc96].

Although each domain-specific safety standard defines a specific vocabulary, it covers the complete safety life-cycle derived from the IEC 61508 [Int98] safety standard. First attempts to identify similarities and dissimilarities of different safety standards have already been performed in [BBBD+10; BABB+12; LABB+12; MBBB+12; PA99]. As a result of these previous analyses the following similarities have be identified:

- Common notion of safety and certification

- Linear progressing safety process with dedicated phases

- Combined hazard assessment and risk analysis to derive safety requirements

- Criticality levels as means to allocate safety (integrity) requirements to system elements

- Verification activities are driven by the safety requirements

- Safety case provides evidence that safety requirements are fulfilled which is needed for certification

Moreover, the following divergences have be identified:

- Varying definition of criticality levels

- Different approaches for the allocation of safety requirements

- Domain-specific verification & validation processes

Based on a number of identified similarities of the safety standards in the transportation sector, [PA99] already outlines a generic safety assessment process integrated into a concrete system development process.

In this document we use the ISO 26262 process as an example for a safety life-cycle, which is based on the well established V-model development life-cycle. However, the results can be transferred to any other safety standard derived from the IEC 61508 safety standard, due to the fact the the safety life-cycle is the same.

# 2.3 The Role of Collaborative Engineering in the Definition of the Design Process

As explained in the introduction, we see a trend firstly toward integrated, heterogeneous functional domains in the automotive and aerospace industries and secondly towards heterogeneous hardware architectures based on capable, centralized hardware platforms. At the level of development processes and collaborations along value chains, these trends imply two things: (1) OEMs and suppliers at several levels of the supplier pyramid must collaborate more closely and intensively than before for successful function integration. (2) In order to make the complexity of the developed software-intensive products manageable, the partners involved depend on a simple and efficient exchange of different development artifacts, such as enabled by AMALTHEA system models.

However, in such heterogeneous communities, typically suppliers collaborate whose business areas overlap. Thus, individual companies are in competition with each other and an open exchange of information is not readily possible due to intellectual property protection concerns.

For this reason, we investigated in PANORAMA what organizational challenges and threats arise for data security in heterogeneous development communities when sharing development artifacts, especially detailed AMALTHEA system models. Based on this analysis, we have conceived recommendations on how to enable a trustful exchange of such development artifacts. Hereto, we conducted a total of four workshops over a period of six months in Q4 2020 and Q1 2021 with partners of the PANORAMA project consortium. We conducted each workshop in an agile manner and academic partners supported their execution methodologically. This means that at the beginning of each workshop, we conceived the respective workshop topics, prioritized them and worked on them jointly. At the end of each workshop, we conducted a review of the workshop results and a retrospective of our joint collaboration in the workshop. This ensured that we were able to work efficiently towards the defined research questions and designed subsequent workshops based on the gained insights. In the course of the workshop series, we developed a fictional, minimal but sufficient and representative engineering scenario. In this scenario, four companies collaboratively develop an advanced driver-assistance system (ADAS) across three stages of the value chain. To analyze the cross-company information exchange, we instantiated the PANORAMA design process multiple times, i.e., per company.

We modeled the identified data security threats by means of the existing threat modeling methods LINDDUN [DWS+10] and STRIDE [HL06]. Our recommendations for data security are based on the international standard ISO/IEC 27010 [ISO15].

We describe our research methodology on data security in collaborative processes and our results in more detail in Deliverable 6.3 [SSK+21].

# 3 Methodology

In order to answer our research questions (cf. Section 1.1), we followed a multi-stage research methodology that involved a number of researchers and industrial and academic partners over a period of several months. Roughly, the methodology incorporated the following steps:

Focus Group to come up with a process description based on typical industrial workflows.

- A Second Focus Group to refine the process with aspects of collaboration and traceability.

- A Survey of Tools and Artifacts typically used in industry and how they are related.

- **Continuous Refinement** over several months by experts to incorporate additional aspects, in particular safety.

- **Creation of Engineering Scenarios** to identify which concrete activities are commonly performed.

- Systematic Analysis of Engineering Scenarios to analyze coverage and identify gaps.

We describe these distinct steps in our methodology in the following.

### 3.1 Focus Group for Process Definition

The first step towards a process description took place as a focus group in which three engineers from three companies were assisted by two researchers in creating a first version of a "big picture" development process description for heterogeneous systems. The main focus of this exercise was to create a description that was independent of a specific safety standard and showed different analysis techniques that would be applied based on a common system model, the AMALTHEA model [HMS+17]. As such, the process description was not complete at this stage and was very high-level. However, it showed a complete life-cycle from requirements engineering, via system design, to system analysis. The analysis results fed back into the system design stage. While the consensus of the engineers was that the process overview is compatible with common standards in the automotive and the avionics domain, no attempt was made to map the activities to these standards.

### 3.2 Focus Group on Collaboration

We conducted a second focus group with seven engineers from five different companies. These companies included an OEM from the avionics industry, a tier-1 supplier (mostly automotive industry), and three tool suppliers. The aim of the focus group was to understand how companies collaborate in a large product development effort, which development activities are conducted jointly and separately, how information is exchanged, and which traceability is established and maintained. In addition, we wanted to better understand how the process description developed in the first focus group fits into a collaborative work environment.

The focus group was prepared by the researchers by providing an interview guide. Two researchers took notes while two other researchers asked the questions, making sure all participants were provided an opportunity to answer every question. The full focus group was recorded and two transcripts were created independently. No major differences in these transcripts were detected.

The transcribed focus group then served as the input to an analysis activity which resulted in the definition of requirements and gaps (cf. Deliverable 6.1 [MCA+20]), but also in a refinement of the process description. We used thematic coding and a workshop among the involved researchers in this process.

#### 3.3 Survey

To get an understanding of which tools are used, which artifacts these tools produce and consume, and which activities these tools support, we sent out a survey to eight tool providers. The tool providers (three academic, five industrial) were asked to answer the following questions:

- What are the model elements (artifacts) consumed/produced by the tool?

- What is the format of each model artifact?

- What are the design steps (activities) where the tool shall be used?

The results were collected in a table that listed the various artifacts and which tools consume/produce them. In addition, a list of activities was synthesized from the answers and matched to the process description, leading to a refinement of it. The tools we collected were also used to extend the process description.

## 3.4 Continuous Refinement

After the initial data collection steps, we worked on the continuous refinement of the process description. Importantly, the development of the MobSTr dataset [SKB+21] provided crucial insight into missing activities, in particular w.r.t. safety activities. All refinements were suggested and discussed by a group of researchers and evaluated with industrial partners that also participated in the initial steps.

The end result of the refinement is a process description that contains all crucial process steps in the development of a heterogeneous system. It remains independent of a concrete safety standard, even though we did perform a mapping to ISO 26262 [Int18] as part of the refinement as presented later in this report.

## 3.5 Creation of Engineering Scenarios

In order to understand how the process description supports common tasks in the engineering of heterogeneous systems, we asked our academic and industrial partners to provide *engineering scenarios*, i.e., standardized descriptions of such common tasks. For this purpose, we created a template that could be filled out by the project partners (cf. Table 3.1). We had pre-filled some of the information for some partners based on other information available to use in the project.

We received twelve engineering scenarios from nine different partners. Since our partners are mainly involved in system analysis, the scenarios are focused on these aspects of the process. The resulting engineering scenarios were discussed with the partners providing tools in order to ensure that they match the tool provider's own view on usage of their tool and methods.

Each Engineering Scenario is presented as an extended *user story* [LDvdWB16]. In general, a user story asks for a *persona* (who is responsible?), a *job to be done* (what is the task to be solved?), the *pain* (what is the problem?), a *pain reliever* (how is the problem solved?), and the *benefit* (from solving the problem). The template is shown in Table 3.1.

| ES-n         | Title: <i>tbd</i> .                                                                                 |                                               |  |

|--------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------|--|

|              | Provider(s): <i>tbd</i> .                                                                           |                                               |  |

| Goal – W     | Goal – What is the goal?                                                                            |                                               |  |

| This sectio  | This section describes the purpose of the PANORAMA tool or method shown in the                      |                                               |  |

| engineerin   | g scenario. It describes on a hi                                                                    | igh level the job to be done, the pain, the   |  |

| pain reliev  | ver (i.e., the tool or method), an                                                                  | nd the <i>benefit</i> .                       |  |

| Activities   | Activities in Focus – Which activities are in focus?                                                |                                               |  |

| This sectio  | This section describes the <i>job to be done</i> and the <i>pain reliever</i> by showing the single |                                               |  |

| activities t | activities that make up the engineering scenario and the data flow between them. In                 |                                               |  |

| particular,  | particular, it is shown which parts of the PANORAMA Design Process (see Chapter 4)                  |                                               |  |

| are suppor   | are supported by the tool/method in the focus of the scenario.                                      |                                               |  |

| Input Ar     | tifacts – Which artifacts are                                                                       | <b>Output Artifacts</b> – Which artifacts are |  |

| consumed?    | 2                                                                                                   | produced?                                     |  |

| This section | on summarizes the input arti-                                                                       | This section summarizes the output ar-        |  |

| facts of th  | facts of the tools used in the scenario. tifacts of the tools used in the scenario.                 |                                               |  |

| The inform   | The information on artifacts and their   The information on artifacts and their                     |                                               |  |

| formats is   | key for forming interoperable                                                                       | formats is key for forming interoperable      |  |

| tool chains  | s that support the process.                                                                         | tool chains that support the process.         |  |

Table 3.1: Template for the Collection of the Engineering Scenarios

**Traceability Information** – Which (cross-model) trace links are used? As identified in the second scenario and also in general in WP6, traceability strongly supports the creation of safety cases. As part of the MobSTr dataset, a traceability information model (TIM) that supports the safety process has already been identified. Since not all tools within PANORAMA have been integrated into MobSTr or provide other traceability information, this section is optional.

**Example Instantiation** – *How can the scenario be applied?*

This section provides an example for application of the tool or method in the context of the engineering scenario. Because not all providers of Engineering Scenarios participated directly in WP6, example instantiations are missing for some of the Engineering Scenarios. The interested reader is referred to the WP3 deliverables and tool presentations for examples in this case.

## 3.6 Analysis of Engineering Scenarios

Once we received the scenarios, we defined different criteria for their analysis. As they are mostly concerned with analysis tasks, we also consider the different activities we conducted in the creation of the MobSTr dataset [SKB+21] as an additional data point. This, in particular, provides additional input for requirements and system design phases which are not well-covered by the engineering scenarios we collected.

As a first step, the collected scenarios were analyzed with regard to their coverage of the design process. For this purpose, the process steps addressed by the engineering scenarios were combined into a common overview. The resulting overview was then used to determine coverage metrics on process level and from the perspective of parts and clauses of the particularly relevant ISO 26262. Based on these results, progress was assessed in comparison to the outcomes of the AMALTHEA4public project.

A second step was a detailed investigation of the (technical) interfaces between the scenarios considered. Here, a special focus was placed on the consideration of the exchange formats and data models used. In the further course of the analysis, commonly used and non-agreed formats were collected separately to identify gaps in the tool chains.

# 4 Design Process

#### 4.1 Approach and Overview

A common design process on which all involved engineers and stakeholders can agree is a key enabler for joint systems development by collaborating heterogeneous organizations. Such a process defines the individual design steps and activities, as well as the required input work products and provided output work products for these steps. A work product can be any design artifact like a document, a model, executable code, or analysis results.

The flow of activities and work products provides a general structure, which must be further substantiated. This includes, among many other things, the roles and responsibilities for the individual activities, suitable quality metrics for the work products, and measures to ensure adherence to these metrics (quality gates). An instantiation also requires a proper definition of the interfaces, such as format and structure of the work products. This in turn provides the basis for establishing traceability between individual design artifacts, which constitutes another important pillar in collaborative system development. All this is strongly entangled with the tools that are used for the development.

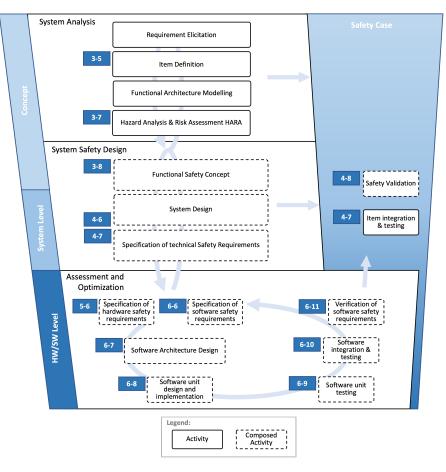

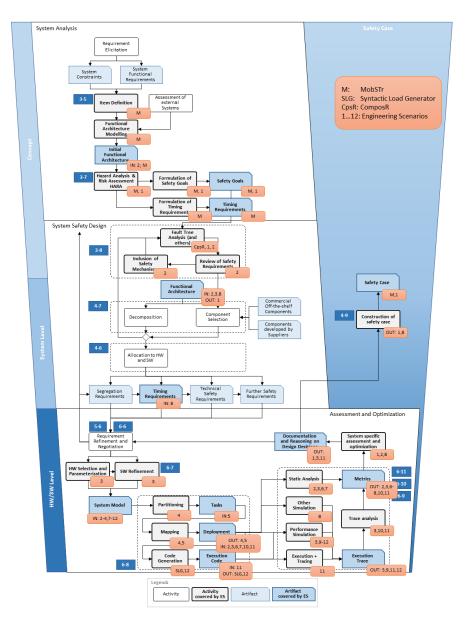

Figure 4.1 depicts a high-level overview of the design process that has been developed in the PANORAMA project. The main objectives of this development can be summarized as follows:

- Definition of a process that covers as many requirements of safety oriented system development as possible;

- Enabling the investigation of aspects of the development as discussed in the previous sections in the context of a research project; and

- Demonstrating the application of collaborative development by instantiating a set of engineering scenarios, including the application of particular tools and the production and exchange of concrete design artifacts.

The resulting process is consistent with the ISO 26262 standard process: The left hand side of Figure 4.1 shows the main design phases *Concept, System Level* and HW/SW Level of the standard. The process also consists of three phases, which are however arranged slightly differently. The *System Analysis* phase subsumes the activities concerning early design steps such as hazard and risk assessment, the definition of system items and elements, and the top-level safety requirements. The labels (dark blue) attached to the activities refer to the corresponding clauses in the ISO 26262 standard. For this first phase, the corresponding clauses belong to the *Concept* phase (Part 3).

Figure 4.1: High-Level Overview of the Design Process

Phase System Safety Design concerns the construction of the functional safety architecture and its decomposition with respect to the hardware/software interfaces. The former corresponds to Clause 3-8 in the ISO 26262 standard, which is located also in the *Concept* phase. As the presented process strongly focuses on model-based design, the engineering activities for constructing the functional safety architecture are supposed to be performed on a functional architecture model and thus have been located in the system design phase.

The specification of technical requirements is the last activity and its output provides the interface to the Assessment and Optimization phase. It is devoted to the design of the technical realization as well as its assessment and optimization. The ISO 26262 standard separates HW and SW level design (Part 5 and 6, respectively). Subsuming them into a single phase reflects the tight connection of these two parts.

The figure reveals that the specified design phases are mostly concerned with the design (left part of the "V") and not with system integration. This is because the project activities are devoted mainly to these phases. Also development on demonstrators that involve system integration took place (cf. [Con22]), which is however out of scope of this handbook. The process nonetheless covers various validation and verification activities.

A particular focus has been put on the construction of safety cases from the individual activities as they constitute a key design artifact in safety oriented design.

## 4.2 Design Phases

In the following, the phases are examined in more detail to shed some light on the involved development activities. Many relevant engineering aspects have been covered in different engineering scenarios. These instantiate this process and are elaborated in Chapter 5. The following discussion relates the individual activities in the process with the corresponding clauses of the ISO 26262 standard in order to give some guidance for readers who are familiar with the standard. Each phase lists some tools that may be used to support the individual activities. Many of them are rephrased from Trei et al. [TMSP16] for additional guidance. Trei et al. also served as input for this report in other aspects and thus is highly recommended related work. Again, Chapter 5 provides deeper insight into potential tools for instantiating the design process.

#### 4.2.1 System Analysis

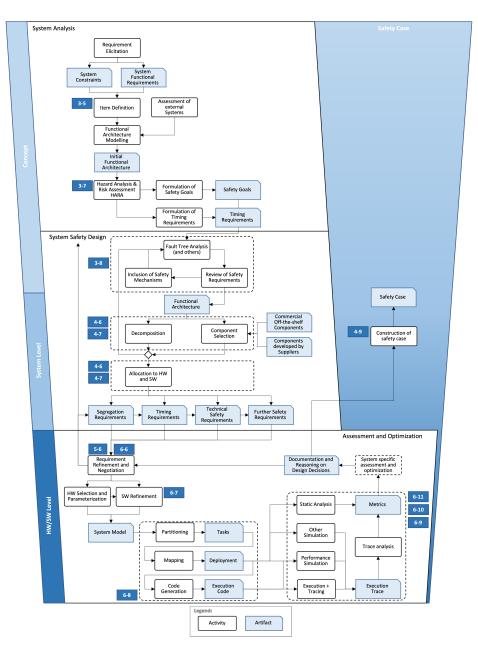

The activities and resulting artifacts of the System Analysis phase are depicted in Figure 4.2. The activity Requirement Elicitation subsumes all steps that define the functional system requirements. They define what the system is supposed to do. The next step is definition of the system items in the Item Definition activity. It corresponds to Clause 3-5 of the ISO standard. There, it is recommended that functional and non-functional requirements shall be available. Hence, this activity is preceded by Requirement Elicitation, which is not explicitly mentioned in the ISO standard. Also not mentioned is the activity that follows, i.e., the decomposition of the system items into an initial functional architecture in the Functional Architecture Modeling activity. A functional architecture has been identified as a suitable structured representation of the system items (cf. [PHAB12]). It may incorporate the results of an Assessment of External Systems, which is otherwise mentioned in the ISO standard as part of the Initiation of the Safety Lifecycle (Clause 3-6).

The following activities concern the early risk assessment, from which the top-level safety requirements are derived. The results of the *Hazard Analysis and Risk Assessment* serve as inputs for the *Formulation of Safety Goals*. Since timing requirements are considered an important part of system design, they have been made explicit in this picture as *Formulation of Timing Requirements*.

**Tools:** The following list is purely informative, in no way complete, and not intended as a recommendation. Each item contains the tool name, followed by the artifact format in parentheses, and the activities/work products.

- APP4MC (AMALTHEA): Requirements, Item Definition, Architecture

- Enterprise Architect (SysML): Requirements, Item Definition, Architecture

Figure 4.2: System Analysis (Phase 1)

- Papyrus (SysML): Requirements, Item Definition, Architecture

- ProR (ReqIF): Requirements, HARA

- Capella/System Modeling Workbench (Arcadia): Requirements, Architecture

- Siemens Capital Systems: Architecture

Figure 4.3: System Safety Design (Phase 2)

- Polarion: Requirements, Item Definition, HARA

- SafeTbox: Requirements, Architecture, HARA, Safety Case Modeling

- Vector PREEvision: Requirements, Item Definition, Architecture, HARA, Safety Case Modeling

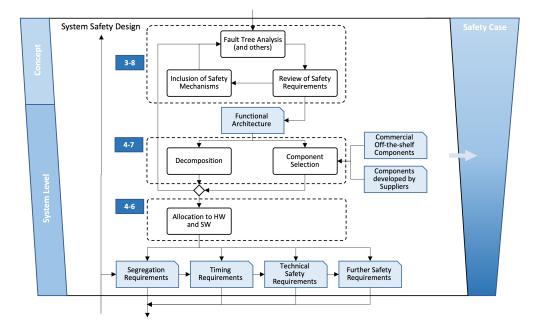

#### 4.2.2 System Safety Design

The second phase System Safety Design is shown in Figure 4.3. It is devoted to develop the (functional) system architecture and to derive the technical requirements for the following HW/SW design. As mentioned above, the construction of the functional safety concept is located in the concept phase of the ISO standard, whereas it belongs to the system design in the process presented here. The reason lies in the intended design flow of the design step: The respective safety requirements are derived in the Fault Tree Analysis and then reviewed (Review Safety Requirements) in order to derive suitable mitigation mechanisms. These mechanisms are directly integrated into the functional architecture model in the Inclusion of Safety Mechanisms activity, which thus can be seen as part of the system design. However, in ISO 26262, this step belongs to Clause 3-7 (Functional Safety Concept).

After this iterative design step is completed, the resulting architecture is decomposed and partitioned in order to prepare the subsequent preliminary allocation to hardware and software in the *Allocation to HW and SW* activity. The *Decomposition* activity is accompanied by a *Component Selection* activity, where components provided by suppliers and other off-the-shelf components are integrated into the design. The aim is to obtain an initial technical realization, often called "logical architecture". These steps correspond to the System Design step (Clause 4-6) in the ISO standard. Additional virtual integration tests can be performed in the activity, which then corresponds to Clause 4-7.

In the Allocation to HW and SW activity, the selection of hardware elements of the system takes place as well as the allocation of the system components to software and hardware. This process imposes new requirements that need to be satisfied by the following phases in order to cover all top-level requirements. This includes safety related requirements such as segregation and diversity properties, as well as refined timing requirements, for example those related to maximal communication latencies. In AUTOSAR, this corresponds to the specification at the Virtual Function Bus (VFB) level [AUT17]. During this process, it may turn out that the initial architecture or previously derived requirements must be modified. Hence, earlier activities may be re-entered to incrementally refine the results if necessary.

**Tools:** The following list is purely informative, in no way complete, and not intended as recommendation. Each item contains the tool name, followed by the artifact format in parentheses, and the activities/work products.

- ProR (ReqIF): Functional Safety Concept

- APP4MC (AMALTHEA): Functional Safety Concept, Decomposition, Allocation

- Enterprise Architect (SysML): Functional Safety Concept, Decomposition, Allocation

- Papyrus (SysML): Functional Safety Concept, Decomposition, Allocation

- Capella/SMW (Arcadia): Functional Safety Concept, Decomposition, Allocation

- Polarion together with Siemens Capital Systems: Functional Safety Concept, Decomposition, Allocation

- SafeTbox: Functional Safety Concept, Fault Tree Analysis (and others), Decomposition, Allocation, Safety Case Modeling

- Vector PREEvision: Functional Safety Concept, Fault Tree Analysis (and others), Decomposition, Allocation, Technical Safety Concept, Safety Case Modeling

- Isograph FaultTree+: Fault Tree Analysis (and others)

- EMFTA: Fault Tree Analysis (and others)

- ALD Fault Tree Analyser: Fault Tree Analysis (and others)

- Fault Tree Analysis on R: Fault Tree Analysis (and others)

Figure 4.4: Assessment and Optimization (Phase 3)

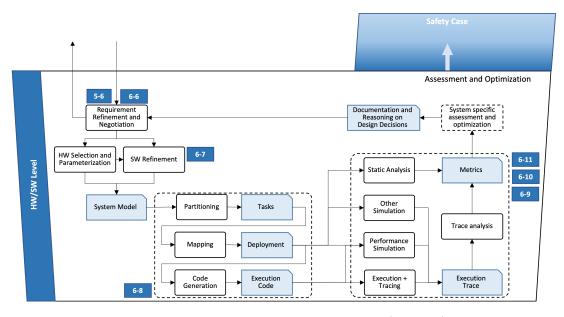

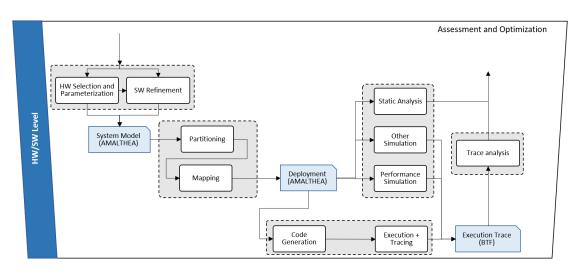

#### 4.2.3 Assessment and Optimization

The main outputs of the System Analysis and the System Safety Design phases, namely requirements and the technical safety architecture, serve as inputs of the final phase Assessment and Optimization. The corresponding design flow illustrated in Figure 4.4 is devoted to the systematic development, refinement, assessment and optimization of heterogeneous hardware/software designs.

Also this phase is designed as an iterative process. At the top left part of Figure 4.4 are the activities located that correspond to the specification of technical requirements and the software architecture design in the ISO standard (clauses 5-6, 6-6 and 6-7). Initially, the *Requirement Refinement and Negotiation* will typically pass the requirements from the previous design phase. Modifications to these requirements may take place in subsequent iterations. The assumption concerning the software architecture design is that the HW*Selection and Parameterization* may affect the developed software architecture, which calls for an optional *SW Refinement* activity.

The resulting architecture then is deployed, which includes the usual *Partitioning* and *Mapping* activities. The *Code Generation* activity aims at the implementation of the actual system functionality. This can happen manually or (semi-)automatically, e.g., using code generators. In the ISO standard, this corresponds to the Software Unit Design and Implementation (Clause 6-8).

The right part of Figure 4.4 shows the activities that are devoted to the assessment of the resulting technical architecture. The activities subsume all test, simulation and analysis methods that apply to this design level. The results of this evaluation phase provide the input to further system optimizations in the *System-specific Assessment and Optimization* activity, which may lead to further iteration loops depending on the overall assessment results.

The development of methods located at this design phase was a main focus of the PANORAMA project. For more information we refer to [Con20b; Con20a; Con20c]. Only shown abstractly in the figure is the fact that the evaluation results serve as a major input to the construction of the safety case (see, e.g., [KW04]).

**Tools:** The following list is purely informative, in no way complete, and not intended as recommendation. Each item contains the tool name, followed by the artifact format in parentheses, and the activities/work products.

- APP4MC (AMALTHEA): HW Selection and Parameterization, Partitioning, Mapping

- Artop (AUTOSAR): HW Selection and Parameterization, Partitioning, Mapping

- Siemens Capital VSTAR (AUTOSAR): HW Selection and Parameterization, Partitioning, Mapping

# 5 Engineering Scenarios

The engineering scenarios described within this chapter have been kindly provided by PANORAMA partners from different work packages, mainly WP1, WP3, and WP6. As described in Chapter 3, the partners were asked to fill in a survey template for engineering scenarios. In order to keep effort in check, some information had been gathered beforehand by the handbook authors from presentations, deliverables, and preliminary surveys within PANORAMA. The following engineering scenarios were collected and are described below:

- Change Impact Analysis (ES-1)

- Enhanced Project Development Life Cycle (ES-2)

- Verification of Consistency and Timing of End-to-End Chains (ES-3)

- Early Design Space Exploration (ES-4)

- Optimization of Task Deployment (ES-5)

- Verification of End-to-End Latency Requirements (ES-6)

- Analysis of Timing Behavior (ES-7)

- Correct Implementation of Safety Mechanisms (ES-8)

- Fault-Tolerant Scheduling Analysis (ES-9)

- Simulation of Timing Behavior (ES-10)

- Trace Analysis for Timing Behavior (ES-11)

- SystemC Performance Simulation (ES-12)

## 5.1 Change Impact Analysis (ES-1)

The engineering scenario can be described as a user story as follows:

As a safety engineering / manager, I need to identify and asses the results of changes in terms of safety in order to ensure that the system remains safe. Usually, this is a manual task in which the all engineering artifacts need to be reviewed. Traceability enables an automated retrieval of artifacts which are affected by a specific change. This will ease the change impact analysis by reducing effort and the possibility of faults.

| Input Artifacts                                                                                                  | Output Artifacts                                                                             |

|------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| • <i>Hazards</i> identified during the Haz-                                                                      | • <i>Hazards</i> changed or newly added                                                      |

| ard & Risk Analysis                                                                                              | (e.g., due to modified ASIL classifi-                                                        |

| <ul> <li>Safety Goals that are derived from<br/>the hazards</li> <li>Safety Requirements derived from</li> </ul> | <ul><li>cation of a hazard)</li><li>System Requirements changed or<br/>newly added</li></ul> |

| the safety goals which result from<br>a safety analysis (e.g., an FMEA)                                          | • <i>Safety Goals</i> which are affected by the change                                       |

| • System Requirements defined by a customer                                                                      | • Safety Requirements which are affected by the change                                       |

| • Safety Analysis (FMEA & FTA)<br>conducted based on the functional<br>or physical system architecture           | • Safety Analysis (FMEA & FTA)<br>which is affected by the change and<br>must be adapted     |

| • Functional/Physical Architecture specified during the design process                                           | • Functional/Physical Architecture which is affected by the change                           |

| • Safety Case constructed based on<br>the information from the design pro-<br>cess                               | • <i>Parts of the safety case</i> which are affected by the change                           |

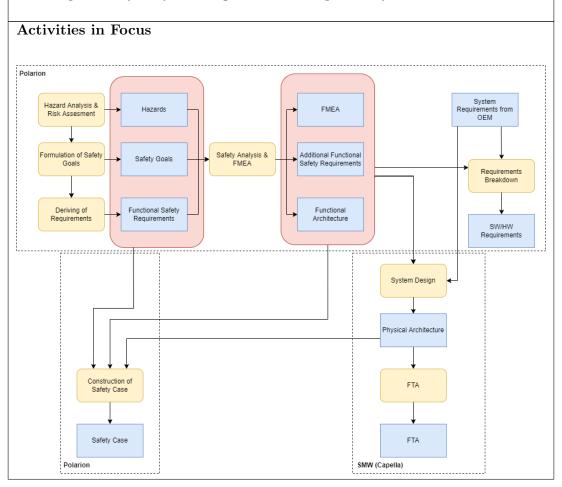

| Traceability Information                                                                                         |                                                                                              |

| -                                                                                                                | ded to the PANORover data set is displayed                                                   |

| in Figure 5.1.                                                                                                   |                                                                                              |

|                                                                                                                  |                                                                                              |

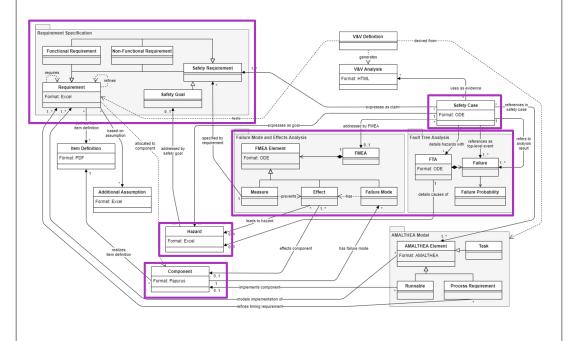

#### Example Instantiation

- 1. Example Instantiation 1 (see Figure 5.2): A new customer requirement is introduced (e.g., enhancement of an ADAS functionality). This leads to new SW/HW requirements. A new HW component must be added in the system architecture, because the old one is not powerful enough to deal with the new task. As a result the safety analyses (FMEA & FTA) must be adapted to the new requirement and the modified system architecture. Moreover, the safety manager must check if the evidence in the safety case still fits the claims. If not, the safety case must be adapted accordingly (e.g., by adapting claims or adding new requirements).

- 2. Example Instantiation 2 (see Figure 5.3): The ASIL assessment of a hazard/safety goal must be adapted (e.g., after discussions with an assessor). As a result, a sensor A must be replaced with sensor B, which also involves the change of a supplier. As a result the safety analyses (FMEA & FTA) must be adapted to the modified safety requirements and the modified system architecture. Moreover, the respective claims in the safety case must be adapted and the safety manager must check if the evidence in the safety case still fits to the modified claims.

Figure 5.1: Traceability Information Used in ES-1

Table 5.1: Engineering Scenario ES-1

## 5.2 Enhanced Project Development Life Cycle (ES-2)

| ES-2                                                      | Title: Enhanced Project Devel                                                      | opment Life Cycle                           |  |  |

|-----------------------------------------------------------|------------------------------------------------------------------------------------|---------------------------------------------|--|--|

| LO-2                                                      | Provider(s): Critical Software                                                     |                                             |  |  |

| Goal                                                      |                                                                                    |                                             |  |  |

| As a Softw                                                | vare Architect/System Engineer                                                     | /Functional Safety Engineer, I want to be   |  |  |

| able to eva                                               | luate how changes impact the sy                                                    | stem safety in early design phases. Typical |  |  |

| document                                                  | -based analysis requires a high                                                    | manual effort and will not cope well with   |  |  |

| system ch                                                 | anges. Integrating an MBSE m                                                       | ethodology into our development process     |  |  |

| will allow                                                | iterating the system design and                                                    | quickly evaluate the overall system safety. |  |  |

| Activities in Focus                                       |                                                                                    |                                             |  |  |

| Fault Tree                                                | Fault Tree Analysis (and others), Review of Safety Mechanisms, Inclusion of Safety |                                             |  |  |

|                                                           | Mechanisms, Static Analysis, System-specific Assessment and Optimization           |                                             |  |  |

| Input Ar                                                  |                                                                                    | Output Artifacts                            |  |  |

| • AM                                                      | ALTHEA model annotated                                                             | • Failure propagation paths (between        |  |  |

| with                                                      | safety-relevant information                                                        | $\operatorname{components})$                |  |  |

|                                                           | Failure/Failure Mode                                                               | • FTA/FMEA (in ODE and Excel                |  |  |

|                                                           | – Failure Probability format)                                                      |                                             |  |  |

|                                                           | • Eclipse Capra with traceability                                                  |                                             |  |  |

|                                                           | links between AMALTHEA and                                                         |                                             |  |  |

| ODE artifacts                                             |                                                                                    |                                             |  |  |

|                                                           | lity Information                                                                   |                                             |  |  |

| Eclipse Ca                                                | Eclipse Capra is used to map between AMALTHEA and ODE components in an             |                                             |  |  |

| attempt to simplify information sharing between partners. |                                                                                    |                                             |  |  |

#### Example Instantiation

A possible instantiation of this engineering scenario can be seen in the following images, where it is assumed that the actor (Safety Engineer) uses the developed tool to load a previously populated AMALTHEA model, and then will perform and observe the following:

- The user navigates to the Architecture View where they will be presented with the system failure propagation paths, obtained from the relationship between all the defined AMALTHEA tasks/runnables (cf. Figure 5.4);

- The user annotates the AMALTHEA model with safety relevant information which was previously obtained from typical HARA activities (cf. Figure 5.5);

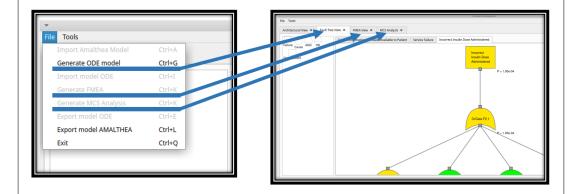

- The user selects the options to generate the safety related artifacts and is presented with dedicated FTA, FMEA and MCS views (cf. Figure 5.6);

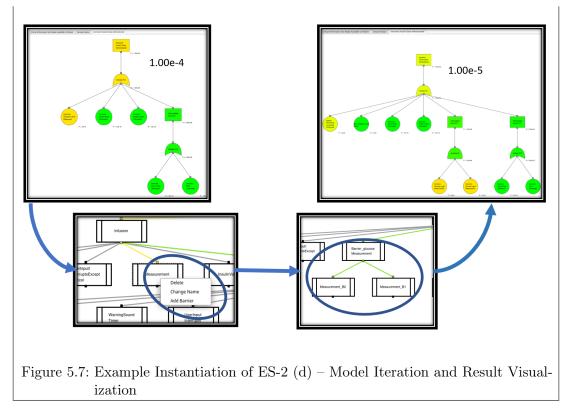

- The user iterates the system design (adds a barrier) and checks in the FTA view that the probability of occurrence of the top/feared event decreased (cf. Figure 5.7).

Figure 5.4: Example Instantiation of ES-2 (a) – Failure Propagation Paths (Architecture View)

| File Tools           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Architectural view × | startup     main     warningSoundRoutine     batteryRoutine       Image: Startup     Image: Startup     Image: Startup     Image: Startup       Image: S |

Figure 5.5: Example Instantiation of ES-2 (b) – Annotation of AMALTHEA Models

Figure 5.6: Example Instantiation of ES-2 (c) – FTA/FMEA/MCS Analysis Views

Table 5.2: Engineering Scenario ES-2

## 5.3 Verification of Consistency and Timing of End-to-End Chains (ES-3)

#### ES-3 Title: Verification of Consistency and Timing of End-to-End Chains Provider(s): INCHRON

#### Goal

To ensure an accurate behavior in an automotive system (especially for autonomous driving), the complete data flow and processing of the information from the sensors up-to the actuators needs to be considered. This includes steps like preprocessing of sensor data, e.g., images from camera systems or radar, extraction of high-level information, e.g., other cars, pedestrians, or obstacles with their positions and movements, a combination of different information to a world picture, reasoning and decisions about actions based on this information and calculation of the resulting actions like trajectories to follow and steering commands to perform. Many of these steps need complex and time consuming calculations. The following aspects are of particular importance:

- the overall latency;

- the variation in the latency (jitter);

- the data ages, especially when merging information from different sources;

- the synchronicity of the different data sources; and

- the consistency of data processing, i.e., whether all data set are processed or the same set of data are processed multiple times.

#### Activities in Focus

Hardware Selection and Parameterization, SW Refinement, Performance Simulation, Trace Analysis, Static Analysis

| Input Artifacts                                                                                                                                          | Output Artifacts                                                                                         |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--|

| AMALTHEA model with the following                                                                                                                        | • End-to-end response time                                                                               |  |

| information:                                                                                                                                             | • Data consistency satisfied                                                                             |  |

| • Software Model:                                                                                                                                        | • Information and visualization of                                                                       |  |

| <ul> <li>model of functions consisting<br/>of the:</li> </ul>                                                                                            | • Information and Visualization of<br>system executions of interest (e.g.,<br>seen worst-case scenarios) |  |

| * function nodes;                                                                                                                                        | ,                                                                                                        |  |

| * the data dependencies be-<br>tween the function nodes;<br>and                                                                                          |                                                                                                          |  |

| * forming event chains de-<br>scribing the data process-<br>ing between input and<br>output (without loops<br>etc.).                                     |                                                                                                          |  |

| - the other (background) soft-<br>ware possibly interfering with<br>the function of above (e.g., lo-<br>cated on the same resource);                     |                                                                                                          |  |

| <ul> <li>the relevant timing informa-<br/>tion on the software mode,<br/>e.g., call frequency (period),<br/>jitter, activation relations etc.</li> </ul> |                                                                                                          |  |

| • Hardware model:                                                                                                                                        |                                                                                                          |  |

| <ul> <li>set of resources as ECUs, mem-<br/>ory;</li> </ul>                                                                                              |                                                                                                          |  |

| - information on the scheduling;                                                                                                                         |                                                                                                          |  |

| – mapping information.                                                                                                                                   |                                                                                                          |  |

| Traceability Information                                                                                                                                 |                                                                                                          |  |

| • Between (latency) requirements and the event chain;                                                                                                    |                                                                                                          |  |

| • Between event chain step and implementation of the (partly) function.                                                                                  |                                                                                                          |  |

Table 5.3: Engineering Scenario ES-3

### 5.4 Early Design Space Exploration (ES-4)

| $\mathbf{ES-4}$ | Title: Early Design Space Exploration |                                            |

|-----------------|---------------------------------------|--------------------------------------------|

| E9-4            | Provider(s): <i>KTH</i>               |                                            |

| Goal            |                                       |                                            |

| The goal i      | s to derive a mapping which sat       | tisfies the design's requirements.         |

| D               |                                       | <b>1</b>                                   |

| • Requ          | uirements include: timing, mem        | ory limits etc.                            |

| • The           | y must be proven during mapping       | ng via formal reasoning.                   |

|                 | , mass se proton danna mappa          |                                            |

| • Map           | ping results can be further asse      | ssed with specific-purpose analysis tools. |

|                 |                                       |                                            |

| Activitie       | s in Focus                            |                                            |

| Partitionin     | ng, Mapping                           |                                            |

| Input Ar        | tifacts                               | Output Artifacts                           |

| • AM.           | ALTHEA system model with              | • The same AMALTHEA System                 |

| "eno            | ugh" information for analytical       | model as before, but refined with          |

| expl            | oration. Enough information           | new mapping entries and possible           |

| inclu           | ides:                                 | extra "tracing".                           |

| _               | proper platform definition;           |                                            |

|                 |                                       | • Estimates from the design space          |

| _               | calculable WCETs;                     | exploration can be optionally at-          |

| _               | proper scheduler definitions          | tached to the model.                       |

| Example         | Instantiation                         |                                            |

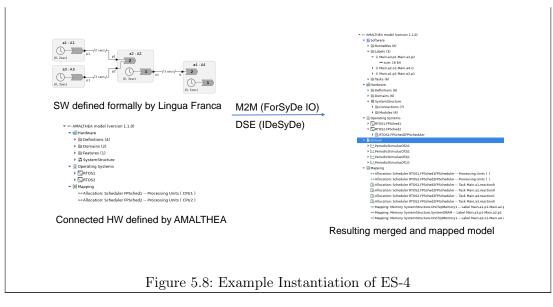

| The tool co     | onsists of model-to-model (M2M)       | ) transformations done with the ForSvDe IO |

The tool consists of model-to-model (M2M) transformations done with the ForSyDe IO tool and design space exploration (DSE) with the tool IDeSyDe. Figure 5.8 shows on the left hand side an example software model in the Lingua Franca format used by the ForSyDe IO and IDeSyDe tools internally, and an AMALTHEA hardware model. On the right hand side, the DSE result in form of a merged AMALTHEA model is shown that contains both the hardware and software model together with a mapping found by the DSE.

Table 5.4: Engineering Scenario ES-4

# 5.5 Optimization of Task Deployment (ES-5)

| ES-5                                                          | Title: Optimization of Task D                                                              | eployment                                   |

|---------------------------------------------------------------|--------------------------------------------------------------------------------------------|---------------------------------------------|

| Provider(s): Dortmund University of Applied Sciences and Arts |                                                                                            | rsity of Applied Sciences and Arts          |

| Goal                                                          |                                                                                            |                                             |

| Optimize                                                      | a given task- to processor deplo                                                           | yment such that the following is satisfied: |

| • no t                                                        | ask misses its deadline; and                                                               |                                             |