Graph Representation and Embedding for Semiconductor Fab States

- Project

- 20212 AISSI

- Type

- New system

- Description

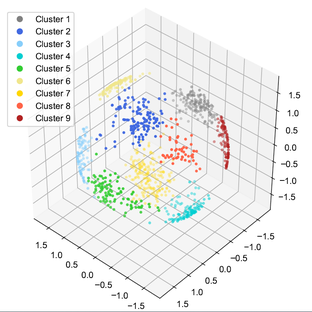

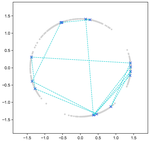

Production planning and control in semiconductor manufacturing fabs necessitate detailed knowledge about the current state of the manufacturing system. By this, it is mandatory to retain structural information between entities. To address this challenge, we develop a graph representation model that captures the interdependencies of machines, lots, and routes. The model comprises the essential procedures in semiconductor manufacturing processes, namely process flows, setup, and maintenance activities. We use representation learning to embed graph snapshots into a low-dimensional space.

- Contact

- Christoph Jacobi

- jacobi@kit.edu

- Research area(s)

- Semiconductor manufacturing, Representation learning, Graph embedding, Generic data model

- Technical features

Graph representations in general and the graph representation approach introduced in this publication can be computationally expensive, for example when being applied on fab or even supply chain level in the semiconductor manufacturing domain. In the field of research on representation learning, different approaches to learn to encode graph structures with embeddings of lower dimensionality are proposed, e.g. embedding the nodes of a graph or entire (sub-)graphs. Therefore, we present a representation learning algorithm that addresses three aspects. First, it enables to encode graphs that represent fab states with embeddings of lower dimensionality and thus allows to handle the computational complexity of graphs. Second, graphs generated using the graph representation model whose size varies can be mapped to an embedding space of fixed dimensionality. Third, learning the graph embedding can be achieved offline, that is, before it is used as input for scheduling or performance analysis tools. This allows efficient exploitation of the results after the model has been trained.

- Integration constraints

The proposed methodology has been applied to the Mini fab model. To apply the graph representation on fab-size level, additional training effort is mandatory.

- Targeted customer(s)

Scholars, researchers, and practitioners for researching purposes

- Conditions for reuse

Everyone is free to use, share, and adapt, if appropriate credit (e.g. citation, indication where changes were made) is given.

- Confidentiality

- Public

- Publication date

- 11-12-2022

- Involved partners

- Robert Bosch GmbH (DEU)

- Karlsruhe Institute of Technology (KIT) (DEU)

- D-SIMLAB Technologies Pte Ltd (SGP)

Images